FPGA Floating-Point Libraries

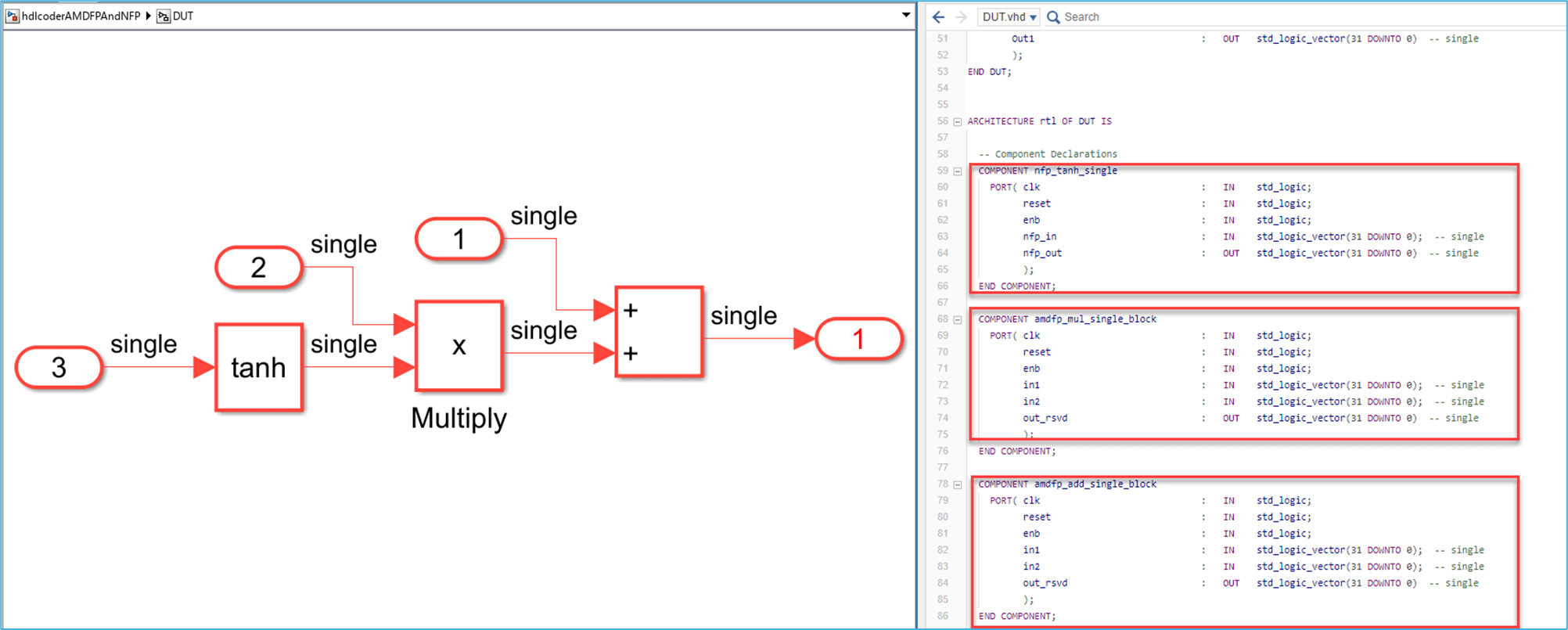

You can map to a floating-point library to synthesize your floating-point design without converting from a floating-point to fixed-point design. Eliminating this conversion step reduces the loss of data precision and enables you to model a wider dynamic range.

If your model design uses Single or Double data

types, use FPGA floating-point target libraries to generate code for your Simulink® model. HDL Coder™ can map your design to the native floating-point library and a vendor-specific

FPGA point library, such as the Altera or Xilinx FPGA floating-point libraries. Using native floating point and vendor-specific

IP together more efficiently uses resources on the FPGA, such as hardened DSP floating point

adder or multiplier primitives, which allows you to fit a bigger design into the FPGA

fabric. This mixed design is advantageous for large and complex models.

Classes

hdlcoder.FloatingPointTargetConfig | Floating-point target configuration for floating-point library |

hdlcoder.FloatingPointTargetConfig.IPConfig | IP settings for selected floating-point configuration |

Topics

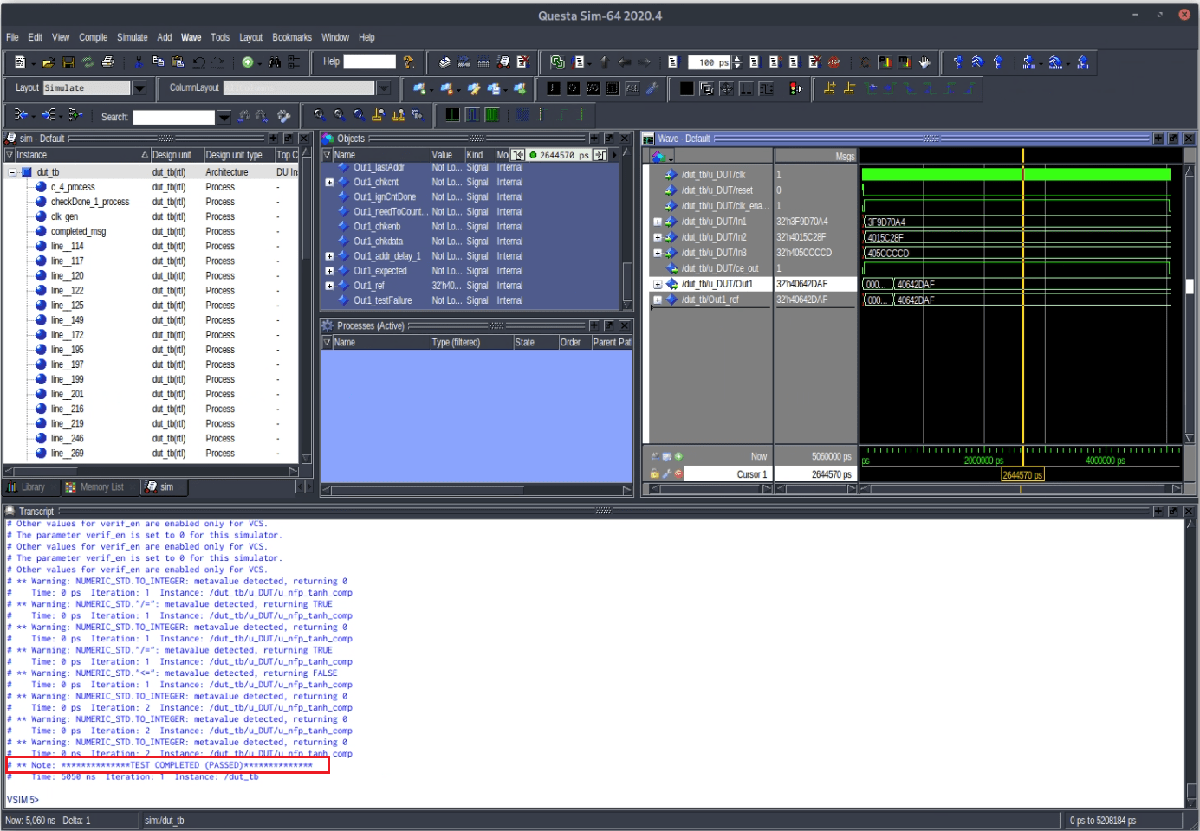

- Generate HDL Code for Vendor-Specific FPGA Floating-Point Target Libraries

How to set up and generate HDL code for Altera and AMD floating-point target libraries.

- Customize Floating-Point IP Configuration

Learn how to customize the latency or target frequency of the floating-point IP library.

- HDL Coder Support for FPGA Floating-Point Library Mapping

Blocks supported in Simulink for mapping to floating-point target libraries.