DVB-S2 HDL PL Header Recovery Using Analog Devices AD9361/AD9364

This example shows how to deploy a Digital Video Broadcasting Satellite Second Generation (DVB-S2) time, frequency, and phase synchronization and PL header recovery algorithm in Simulink®. You use SoC Blockset™ workflow targeted on a Xilinx® Zynq® ZC706 SoC ZC706 evaluation kit connected with an Analog Devices® AD-FMCOMMS3-EBZ SDR board.

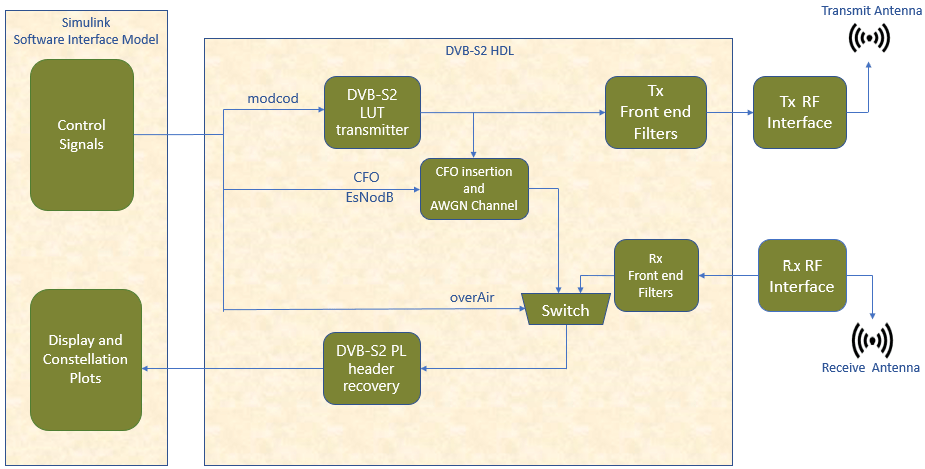

This example uses the PL header recovery implementation from the DVB-S2 HDL PL Header Recovery (Wireless HDL Toolbox) example to deploy a hardware-software (HW/SW) co-design implementation targeted on the Analog Devices AD9361/AD9364 radio platform. This figure shows an overview of the example.

DVB-S2 modems operate in the C (4-8 GHz), Ku (12-18 GHz) and Ka (26-40 GHz) frequency bands. According to the DVB-S2 standard, the satellite transponder bandwidth ranges from 1 MHz to 72 MHz. The model in this example operates at a symbol rate of 25 Mbaud with a root raised cosine (RRC) filter roll-off factor of 0.35. For a MATLAB® implementation of an end-to-end DVB-S2 receiver, see the End-to-End DVB-S2 Simulation with RF Impairments and Corrections (Satellite Communications Toolbox) example. To make this setup work with the SoC blockset workflow, you must install and configure additional support packages and third-party tools.

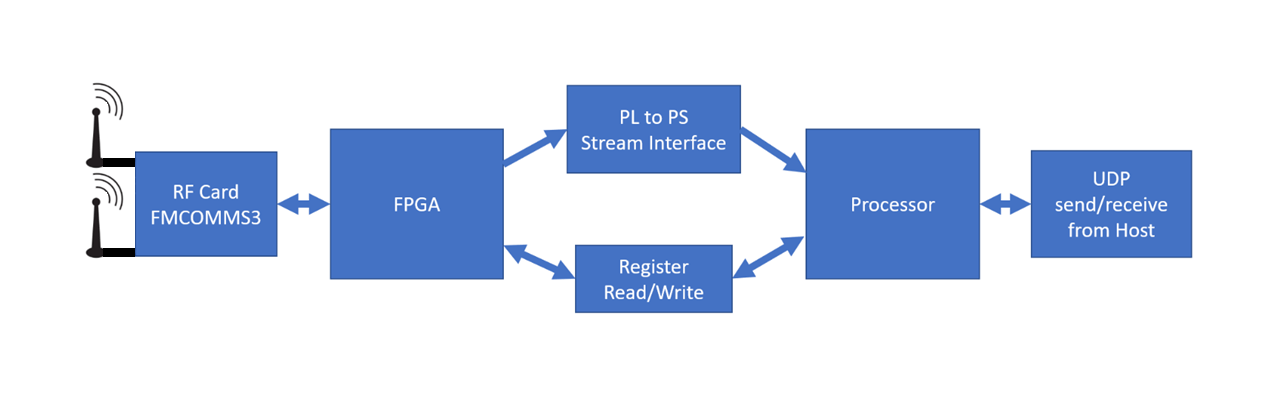

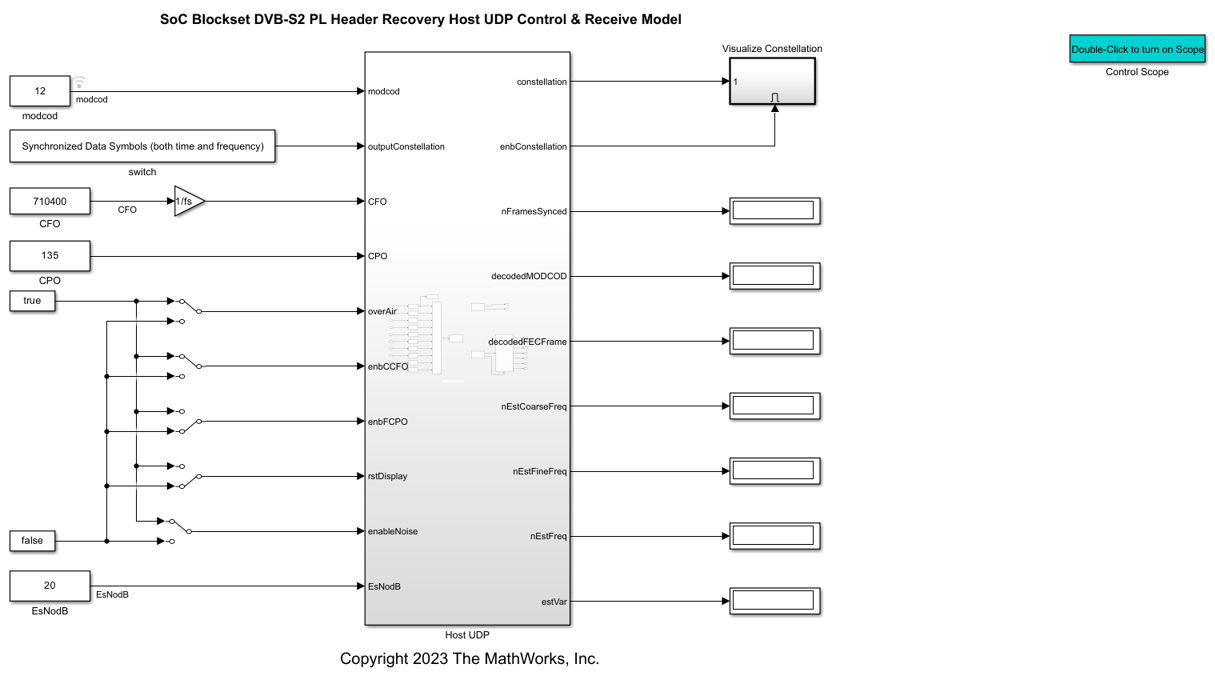

Model Overview This figure shows a simplified functional block diagram of the model.

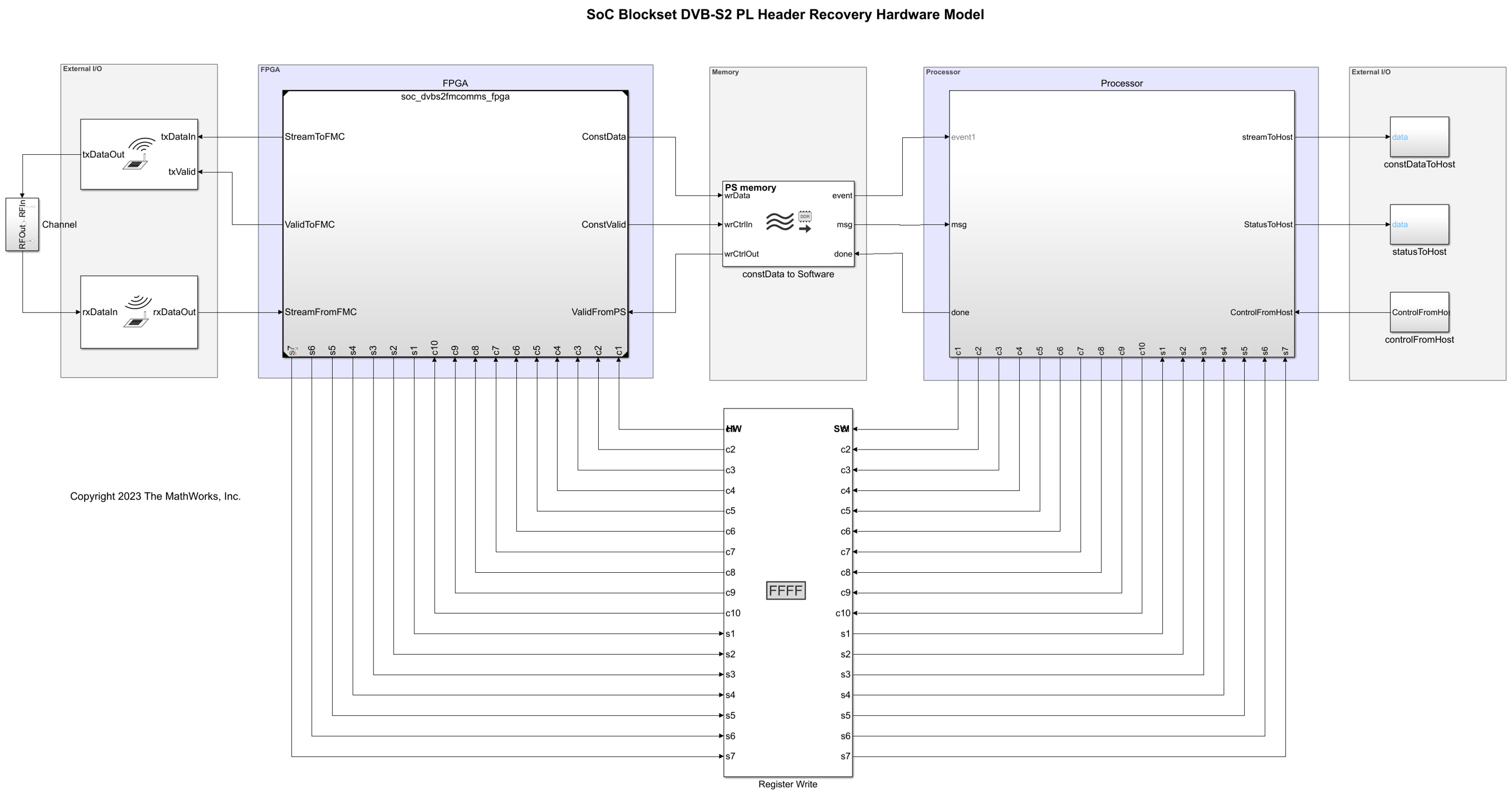

The top model includes the FPGA model soc_dvbs2_fpga and the processor model soc_dvbs2_proc as model references. The top model also includes an AXI4-Stream to Software block that shares the external memory between the FPGA and the processor. The model also contains AD9361Tx and AD9361Rx blocks for streaming the data to and from the RF card.

open_system("soc_dvbs2fmcomms_top")

The DVB-S2 algorithm generates the baseband data. The FMCOMMS transmitter receives the data and upconverts it to 2.4GHz frequency. The RF output from the transmitter connects to the receiver through a loopback cable. The FMCOMMS receiver downconverts the received RF signal and then feeds it back to DVB-S2 receiver algorithm. The AD9361Tx and AD936xRx blocks in the top model represent the data streaming path from the transmitter to the receiver.

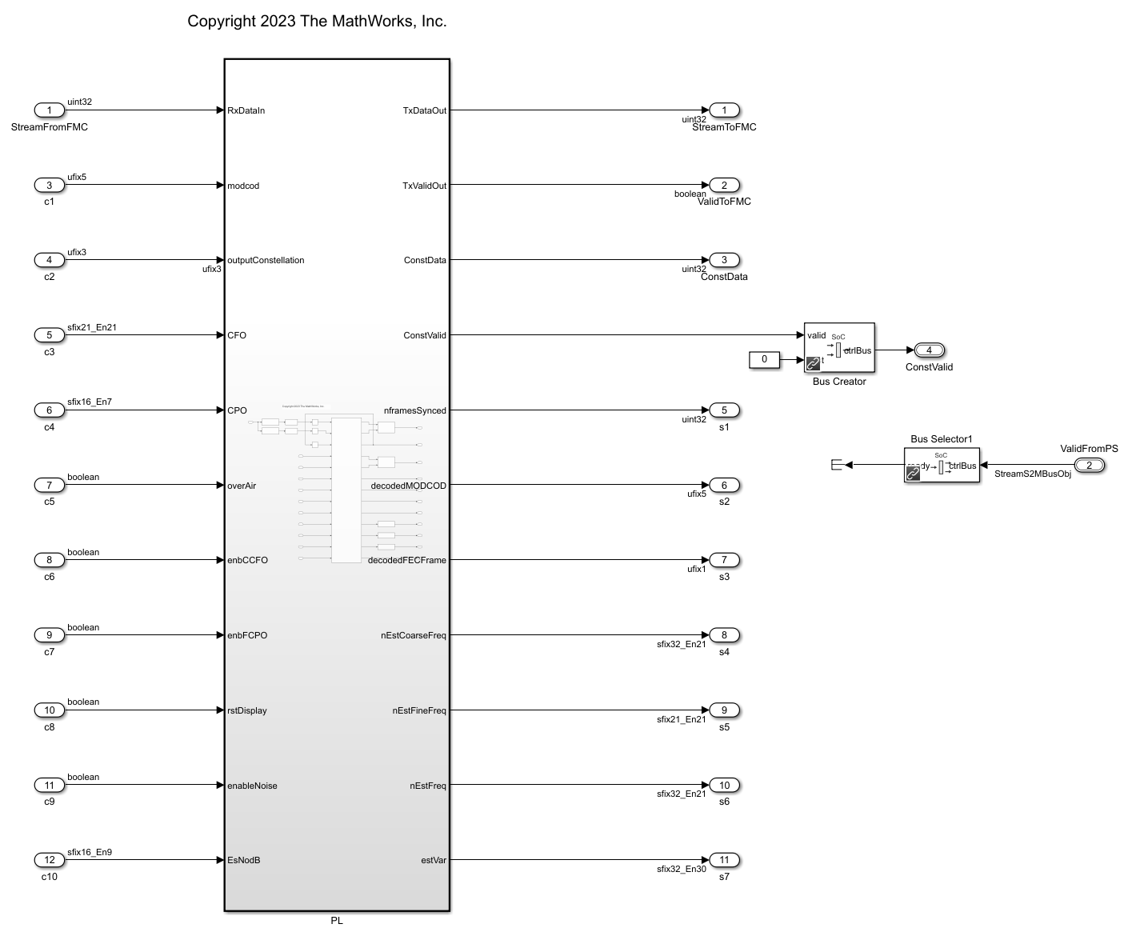

The FPGASystem subsystem in the soc_dvbs2_fpga FPGA model contains DVB-S2 PL Header Recovery HDL algorithm.

open_system("soc_dvbs2fmcomms_fpga")

The DVB-S2 PL Header Recovery HDL subsystem, which is based on the DVB-S2 HDL PL Header Recovery (Wireless HDL Toolbox) example, adds additional functionality to integrate the model with the Zynq® hardware architecture. This PL Header Recovery algorithm sends the received constellation data and the status signals to the processor.

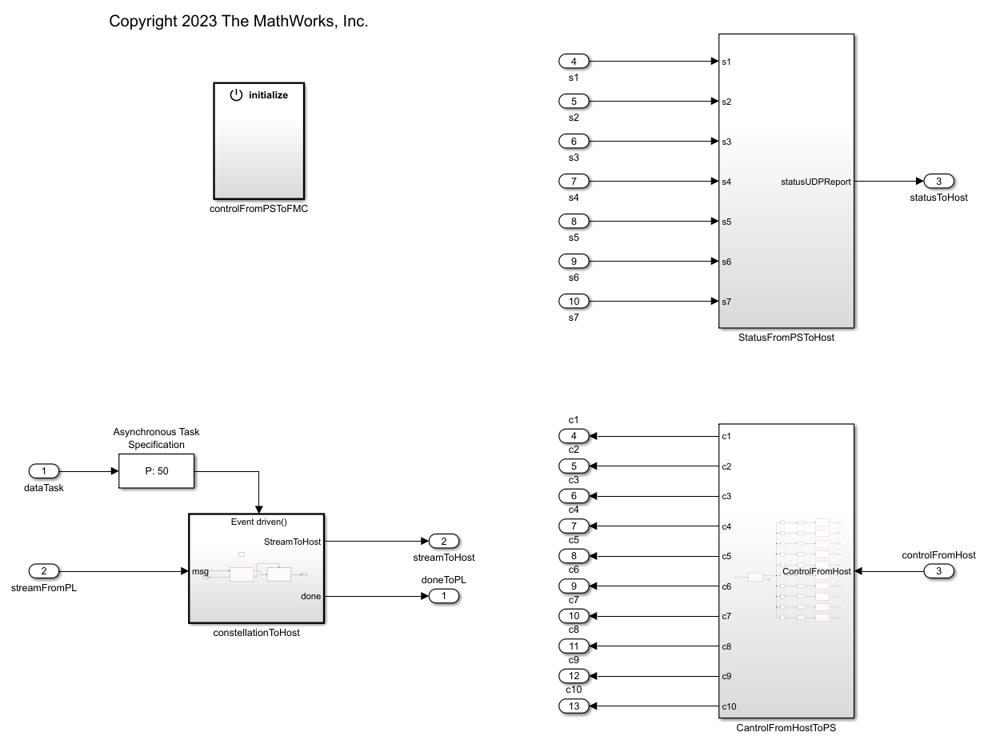

The processor logic contains a read task and a periodic task. The periodic task is a timer-driven task with a period of 0.01, defined in the task manager. The periodic task drives the control and status signals of the hardware algorithm through the AXI4-Lite registers. The model displays status information. The controller provides the constellation data and status information to the MATLAB host through UDP blocks. The Rx UDP Write and Status UDP Write subsystems relay the constellation and status signals, respectively, to the host over the UDP protocol. The read task is an event-based task driven by the arrival of data from the FPGA through DDR memory. This data comprises the constellation data of the selected modulation type. The Processor Algorithm Wrapper subsystem in the soc_dvbs2_proc models these tasks. The tasks connect to the Task Manager block at the top level.

open_system("soc_dvbs2fmcomms_proc")

The processor sends the DVB-S2 PL Header Recovery HDL block output data and receiver status signals directly back to the host over the Ethernet link using UDP. You must set the IP address of the UDP Write block in the processor model to the IP address of the host. This interface model, which runs on the host, shows how to receive data from the hardware platform and how to postprocess it.

open_system("soc_dvbs2fmcomms_host")

Configurations to simulate DVB-S2 PL Header Recovery:

Run the hardware generation model. The model callback initialization function soc_dvbs2_init loads default parameters, all required variables and parity matrices to the workspace. To access the callback initialization, select MODELING > Model Settings > Model Properties > Callbacks > InitFcn. The HDL-optimized blocks in the model requires sample-based signal simulation, so the simulation takes 10-15 minutes to complete. During simulation, you can change input and parameter values. You can also enable or disable over-the-air transmission, carrier frequency offset(CFO), carrier phase offset(CPO) and noise.

Implement & run header recovery algorithm:

To implement and run the algorithm on the target hardware, follow these steps.

1. Connect the SMA cable on the FMCOMMS card to complete the loopback between the transmitter and receiver.

2. Set the Hardware Board option to Xilinx Zynq ZC706 evaluation kit on the System on Chip tab of the Simulink toolstrip.

3. Implement the model on a supported SoC board using the SoC Builder tool. To open SoC Builder, click Configure, Build, & Deploy.

4. On the Setup screen, select Build Model and click Next.

5. Select Build and load for external mode and select Automate build process. Then, click Next.

6. Check the compatibility of the model for implementation

7. Build the model and complete synthesis, implementation and bitstream generation. FPGA synthesis often takes more than 30 minutes. To run this example using a pregenerated bitstream, follow these steps:

a) Close the external shell to terminate FPGA synthesis.

b) Copy the pregenerated bitstream to your project folder by entering this command at the MATLAB command prompt.

copyfile(fullfile(matlabshared.supportpkg.getSupportPackageRoot, ... "toolbox","soc","supportpackages","xilinxsoc","xilinxsocexamples", ... "bitstreams","soc_dvbs2_top-XilinxZynqZC706EvaluationKit.bit"),"./soc_prj");

8. Load bitstream and run the model on the SoC board.

Results: When the host interface model runs successfully, the model displays the constellation diagram and status signals.

See Also

Blocks

- AXI4-Stream to Software | Register Channel | Register Write | Stream Read | Task Manager | UDP Read (HOST) | UDP Write