Binary Weighted DAC

N-bit DAC based on R-2R weighted resistor architecture

Libraries:

Mixed-Signal Blockset /

DAC /

Architectures

Description

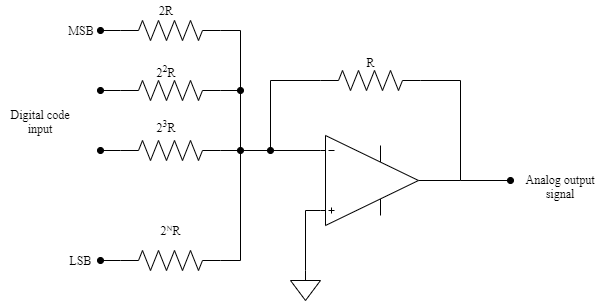

The R-2R DAC is one of the most common types of Binary-Weighted DACs. It consists of a parallel binary-weighted resistor bank. Each digital level is converted to an equivalent analog signal by the resistor bank.

The input/output transfer curve of the binary weighted DAC can be nonmonotonic, which means that the transfer curve can reverse its direction.

The R-2R DAC architecture is low resolution and consumes more power due to the large number of resistors required to implement the architecture.

Examples

This example shows how to find the offset and gain errors of a binary weighted DAC block.

Open the model dac_dc_error. The model consists of a Binary Weighted DAC block and a DAC Testbench.

model = 'dac_dc_error';

open_system(model)

The parameters under the General tab of the Binary Weighted DAC are kept at their default values. The impairments are enabled in the Impairments tab, and the value of the offset error and gain error are set to 2 LSB and 1 LSB, respectively.

In the DAC Testbench block, the Measurement option is set to DC. In the Setup tab, the Autofill setup parameter button is used to automatically propagate the setup parameters from the DAC block. In the Target Metric tab, the Autofill target metric button is used to automatically set the target offset and gain errors from the DAC block. All other parameters are kept at their default values.

Run the simulation for 3.2e-04 s. The measured offset and gain errors are 2.00 LSB and 1.00 LSB, respectively.

The DAC transfer curve matches the best linear fit method. Using best fit method, maximum INL is 0.00034 LSB and maximum DNL is 0.00038 LSB.

This example shows how to find the AC performance metrics such as SNR, SINAD, SFDR, ENOB, noise floor and settling time of a binary weighted DAC block.

Open the model dac_ac_error. The model consists of a Binary Weighted DAC block and a DAC Testbench.

model = 'dac_ac_error';

open_system(model)

The parameters of the Binary Weighted DAC are kept at their default values.

In the DAC Testbench block, the Measurement option is set to AC. In the Setup tab, the Autofill setup parameter button is used to automatically propagate the setup parameters from the DAC block. Show spectrum analyzer during simulation option is also checked.

Run the simulation for 9e-3 s.

sim(model);

The measured AC performance metrics are displayed on the DAC Testbench block.

Ports

Input

Digital input signal to DAC, specified as an integer.

If the Input polarity parameter is set to

Bipolar, the allowed range of the signal is

[−2(NBits-1),

2(NBits-1)-1].

If the Input polarity parameter is set to

Unipolar, the allowed range of the signal is [0,

2NBits-1].

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

External clock to start conversion, specified as a scalar. The digital-to-analog conversion process starts at the rising edge of the signal at the start port.

Dependencies

To enable this port, select Use external start clock in the General tab.

Data Types: double

Output

Converted analog output signal, returned as a scalar.

Data Types: double

Indicates whether the digital-to-analog conversion is complete, returned as a scalar.

Dependencies

To enable this port, select Show ready port in the General tab.

Data Types: double

Parameters

General

Number of bits in the input word, specified as a unitless positive real integer. Number of bits determines the resolution of the DAC.

Programmatic Use

Block parameter:

NBits |

| Type: character vector |

| Values: positive real integer |

Default:

5 |

Data Types: double

Polarity of the input signal to the DAC.

Programmatic Use

Block parameter:

Polarity |

| Type: character vector |

Values:

Bipolar|Unipolar |

Default:

Bipolar |

Select to connect to an external start conversion clock. By default, this option is selected. If you deselect this option, a Sampling Clock Source block inside the Segmented DAC is used to generate the start conversion clock

Frequency of the internal start conversion clock, specified as a real scalar in Hz. The Conversion start frequency parameter determines the conversion rate at the start of conversion.

Dependencies

To enable this parameter, deselect Use external start clock.

Programmatic Use

Block parameter:

StartFreq |

| Type: character vector |

| Values: positive real scalar |

Default:

1e6 |

Data Types: double

Reference voltage of the DAC, specified as a real scalar in volts. Reference (V) helps determine the output from the input digital code, Number of bits, and Bias (V) using the equation:

.

Programmatic Use

Block parameter:

Ref |

| Type: character vector |

| Values: real scalar |

Default:

2 |

Data Types: double

Bias voltage added to the output of the DAC, specified as a real scalar in volts. Bias (V) helps determine the output from the input digital code, Number of bits, and Reference (V) using the equation:

.

Programmatic Use

Block parameter:

Bias |

| Type: character vector |

| Values: real scalar |

Default:

0 |

Data Types: double

Select to enable the ready port on the block. This option is deselected by default.

Impairments

Select to enable impairments such as offset error and gain error in DAC simulation. This parameter is selected. by default.

Shifts quantization steps by a specific value, specified as a scalar in %FS (percentage full scale), FS (full scale), or LSB (least significant bit).

Offset error is applied before Reference (V) and Bias (V).

Note

The full scale range of the converter is defined as the difference between the last and first code on the +0.5 LSB compensated transfer curve. In a +0.5 LSB compensated transfer curve, first code is 0.5 LSB wide while the last code is 1.5 LSB wide. The input values must be considered within the full scale range of the converter.

Note

LSB is calculated by the equation .

Dependencies

To enable this parameter, select Enable linearity impairments in the Impairments tab.

Programmatic Use

Block parameter:

OffsetError |

| Type: character vector |

| Values: real scalar |

Default:

0 LSB |

Data Types: double

Error in the slope of the straight line interpolating the DAC transfer curve, specified as a real scalar in %FS (percentage full scale), FS (full scale), or LSB (least significant bit).

Gain error is applied before Reference (V) and Bias (V).

Note

The full scale range of the converter is defined as the difference between the last and first code on the +0.5 LSB compensated transfer curve. In a +0.5 LSB compensated transfer curve, first code is 0.5 LSB wide while the last code is 1.5 LSB wide. The input values must be considered within the full scale range of the converter.

Note

LSB is calculated by the equation .

Dependencies

To enable this parameter, select Enable linearity impairments in the Impairments tab.

Programmatic Use

Block parameter:

GainError |

| Type: character vector |

| Values: real scalar |

Default:

0 LSB |

Data Types: double

Select to enable timing impairments such as settling time or slew rate in DAC simulation. This parameter is selected. by default.

Specify whether the Binary Weighted DAC calculates switch timing using the settling time parameters or the slew rate parameters.

Dependencies

To enable this parameter, select Enable timing impairments in the Impairments tab.

The time required for the output of the DAC to settle to within some fraction of its final value, specified as a nonnegative real scalar in seconds.

Dependencies

To enable this parameter, select Enable timing impairments

and set Specify switch timing using to

Settling time in the Impairments

tab.

Programmatic Use

Block parameter:

SettlingTime |

| Type: character vector |

| Values: real scalar |

Default:

2e-7 |

Data Types: double

The tolerance allowed for calculating settling time, specified as a positive real scalar in LSB. The output of the DAC must settle within the Settling time tolerance (LSB) by Settling time (s).

Dependencies

To enable this parameter, select Enable timing impairments

and set Specify switch timing using to

Settling time in the Impairments

tab.

Programmatic Use

Block parameter:

SettlingTimeTolerance |

| Type: character vector |

| Values: positive real scalar |

Default:

0.5 |

Data Types: double

Switch the rising slew rate for the DAC, specified as a positive real scalar or vector. If Rising slew rate is scalar, it specifies the same slew rate for all the switches. If Rising slew rate is a vector of length Nbits, it specifies the slew rate for each individual switch.

Dependencies

To enable this parameter, select Enable timing impairments

and set Specify switch timing using to Slew

rate in the Impairments tab.

Programmatic Use

Block parameter:

RisingSlewRate |

| Type: character vector |

| Values: positive real scalar | positive real vector |

Default:

5015625 |

Switch the falling slew rate for the DAC, specified as a positive real scalar or vector. If Falling slew rate is scalar, it specifies the same slew rate for all the switches. If Falling slew rate is a vector of length Nbits, it specifies the slew rate for each individual switch.

Dependencies

To enable this parameter, select Enable timing impairments

and set Specify switch timing using to Slew

rate in the Impairments tab.

Programmatic Use

Block parameter:

FallingSlewRate |

| Type: character vector |

| Values: negative real scalar | negative real vector |

Default:

-5015625 |

Version History

Introduced in R2020a

See Also

DAC Testbench | DAC DC measurement | DAC AC measurement | inldnl

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)