Communicate with the Programmable Logic IP Core on AMD Zynq Board by Using AXI4-Lite Protocol

This example shows how to communicate with the programmable logic IP core on an AMD Zynq® board by using the Advanced eXtensible Interface 4 Lite (AXI4®-Lite) protocol.

Introduction

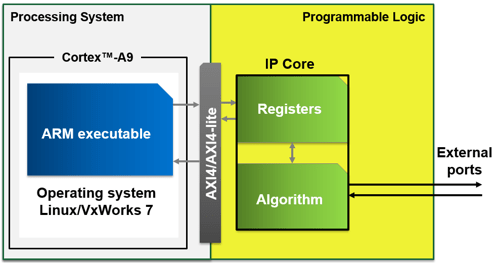

This example shows how to build, deploy, and run a Simulink® model as an ARM® executable on an AMD Zynq processor that communicates with the programmable logic IP core using the AXI4-Lite protocol. The AMD Zynq processor family contains a dual-core ARM Cortex-A processor with Artix®-7 or Kintex®-7 programmable logic. On these devices, the processor is connected to the programmable logic via an AXI4-Lite interface. This example is the final step of integration in the hardware-software co-design workflow for an AMD Zynq board. For more information on the hardware-software co-design workflow, see Get Started with IP Core Generation from Simulink Model (HDL Coder).

Requirements

Simulate the Programmable Logic IP Core Model

This section shows how to configure the Simulink model to send and receive data from the programmable logic IP core. This figure shows the architecture of the FPGA IP core that is connected to the processor through an AXI4-Lite interface. The ARM executable controls the AXI4-Lite accessible (memory-mapped) registers and tunes the parameters of the algorithm in the IP core.

1. Open the FPGA IP core simulation model. The led_counter subsystem represents the logic of the FPGA IP core. The FPGA IP core and bitstream are pregenerated. To customize this design and to generate your FPGA IP core using HDL Coder®, follow the workflow in the Get Started with IP Core Generation from Simulink Model (HDL Coder) example.

2. On the Modeling tab of the Simulink Toolstrip, click Run. The counter waveforms in the scope. The Read_back output of the led_counter subsystem counts from 1 to 255 in steps of (2^n-1).

Configure the Simulink Model to Generate ARM Executable

This section shows how to configure the model to build, deploy, and run an ARM executable on the processor of an AMD Zynq board.

1. Open the zynq_axi4lite_codegen model.

2. Open the led_counter subsystem block.

3. On the Simulation tab of the Simulink Toolstrip, click Library Browser.

4. In the Simulink Library Browser window, select Embedded Coder Support Package for AMD SoC Devices library.

5. Replace each yellow annotation in the led_counter subsystem model by following the instructions provided in the annotation, respectively. This table shows the programmable logic IP core registers mapping for the led_counter subsystem. The offset address values are derived from this table.

For convenience, a zynq_axi4lite_cg_preconf model is provided. This model can generate code for AMD Zynq board running a Linux® operating system. For information on using other operating systems, see Getting Started with VxWorks 7 on AMD Zynq Boards.

Control FPGA IP Core from ARM Executable

This section shows how to build, deploy, and run the Simulink model in external mode and control the programmable logic IP core on an AMD Zynq-7000 SoC ZC702 Evaluation Kit. The executable running on the hardware blinks the LEDs, shown in the figure of step 1, connected to the programmable logic.

1. Run the hardware setup for the AMD Zynq board. For information on the hardware setup, see Install Support for AMD SoC Boards.

2. In the zynq_axi4lite_codegen model, double-click the Program FPGA subsystem block to automatically download a pregenerated bitstream to the programmable logic.

3. On the Hardware tab of the Simulink Toolstrip, click Monitor & Tune to start the external mode simulation. Wait for the model to build, deploy, and run as an executable on the hardware. Once the simulation starts, the waveforms on the scope show the counter waveform from the Simulate the Programmable Logic IP Core Model section.

4. Double-click the Slider gain and Manual Switch blocks to control the speed and direction of the counter, respectively.

5. Stop the external mode simulation by clicking Stop on the Hardware tab.