Get Started with IP Core Generation from Simulink Model

This example shows how to use the hardware-software co-design workflow to blink LEDs at various frequencies on the Xilinx® Zynq® ZC702 evaluation kit.

Video Walkthrough

For a walkthrough of this example, watch the video.

Introduction

This example is a step-by-step guide that helps you use HDL Coder™ to generate a custom HDL IP core which blinks LEDs on the Xilinx Zynq ZC702 evaluation kit, and shows how to use Embedded Coder® to generate C code that runs on the ARM® processor to control the LED blink frequency.

You can use MATLAB® and Simulink® to design, simulate, and verify your application, perform what-if scenarios with algorithms, and optimize parameters. You can then prepare your design for hardware and software implementation on the Zynq-7000 AP SoC by deciding which system elements will be performed by the programmable logic, and which system elements will run on the ARM Cortex®-A9.

Using the guided workflow shown in this example, you automatically generate HDL code for the programmable logic using HDL Coder, generate C code for the ARM using Embedded Coder, and implement the design on the Xilinx Zynq Platform.

In this workflow, you perform the following steps:

Set up your Zynq hardware and tools.

Partition your design for hardware and software implementation.

Generate an HDL IP core using HDL Workflow Advisor.

Integrate the IP core into a Xilinx Vivado® project and program the Zynq hardware.

Generate a software interface model.

Generate C code from the software interface model and run it on the ARM Cortex-A9 processor.

Tune parameters and capture results from the Zynq hardware using External Mode.

For more information, refer to other more advanced examples, and the HDL Coder and Embedded Coder documentation.

Requirements

Xilinx Vivado Design Suite, with supported version listed in the HDL Language Support and Supported Third-Party Tools and Hardware.

Xilinx Zynq-7000 SoC ZC702 Evaluation Kit

HDL Coder Support Package for AMD FPGA and SoC Devices

Set Up Zynq Hardware and Tools

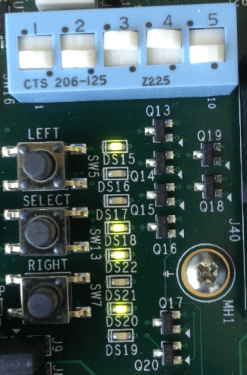

1. Set up the Xilinx Zynq ZC702 evaluation kit as shown in the figure below. To learn more about the ZC702 hardware setup, refer to AMD documentation.

2. Make sure the SW16 switch is set as shown in the figure below, so you can boot Linux® from the SD card.

3. Make sure the SW10 switch (JTAG chain input select two-position DIP switch) is set as shown in the figure below, so you can use the Digilent USB-to-JTAG interface (U23). Position 1 is off and Position 2 is on.

4. Connect your computer to the USB UART connector using a Micro-USB cable. Make sure your USB device drivers, such as for the Silicon Labs CP210x USB to UART Bridge, are installed correctly. If not, search for the drivers online and install them.

5. Connect your computer and the Zynq board using an Ethernet cable.

6. Install the HDL Coder Support Package for AMD FPGA and SoC Devices if you haven't already. To start the installer, go to the MATLAB toolstrip and click Add-Ons > Get Hardware Support Packages. For more information, see Install Support for AMD SoC Boards (Embedded Coder).

7. Make sure you are using the SD card image provided by the HDL Coder Support Package for AMD FPGA and SoC Devices. If you need to update your SD card image, see the Hardware Setup section of Install Support for AMD SoC Boards (Embedded Coder).

8. Set up the Zynq hardware connection by entering the following command in the MATLAB command window:

h = zynq

The zynq function logs in to the hardware via COM port and runs the ifconfig command to obtain the IP address of the board. This function also tests the Ethernet connection.

9. You can optionally test the serial connection using the following configuration using a program such as PuTTY™. Baud rate: 115200; Data bits: 8; Stop bits: 1; Parity: None; Flow control: None. You should be able to observe Linux booting log on the serial console when you power cycle the Zynq board. You must close this serial connection before using the zynq function again.

10. Set up the Xilinx Vivado synthesis tool path using the hdlsetuptoolpath command in the MATLAB command window. Use your own Vivado installation path when you run the command.

hdlsetuptoolpath('ToolName', 'Xilinx Vivado', 'ToolPath', vivadopath);

Partition Design for Hardware and Software Implementation

The first step of the Zynq hardware-software co-design workflow is to decide which parts of your design to implement on the programmable logic, and which parts to run on the ARM processor.

Group all the blocks you want to implement on programmable logic into an atomic subsystem. This atomic subsystem is the boundary of your hardware-software partition. All the blocks inside this subsystem are implemented on programmable logic, and all the blocks outside this subsystem run on the ARM processor.

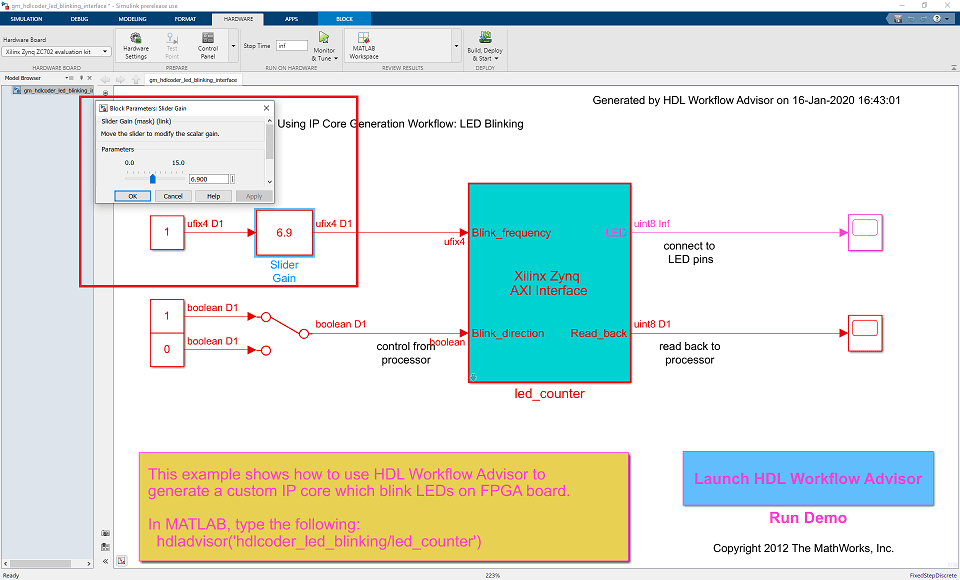

In this example, the subsystem led_counter is the hardware subsystem. It models a counter that blinks the LEDs on an FPGA board. Two input ports, Blink_frequency and Blink_direction, are control ports that determine the LED blink frequency and direction. All the blocks outside of the subsystem led_counter are for software implementation.

In Simulink, you can use the Slider Gain or Manual Switch block to adjust the input values of the hardware subsystem. In the embedded software, this means the ARM processor controls the generated IP core by writing to the AXI interface accessible registers. The output port of the hardware subsystem, LED, connects to the LED hardware. The output port, Read_Back, can be used to read data back to the processor.

open_system('hdlcoder_led_blinking');

Generate HDL IP Core

You can generate a reusable IP core module from a Simulink model using HDL Coder. The generated IP core is designed to be connected to an embedded processor on an FPGA device. HDL Coder generates HDL code from the Simulink blocks, and also generates HDL code for the AXI interface logic that connects the IP core to the embedded processor. HDL Coder packages the generated files into a folder you specify. You can then integrate the generated IP core with a larger FPGA embedded design in the Xilinx Vivado environment.

For an overview of how to generate an IP core for a specific hardware platform, see Targeting FPGA & SoC Hardware Overview. For more information on different ways to generate an IP core using HDL Coder, see Comparison of IP Core Generation Techniques.

Prepare Model for IP Core Generation

To generate an IP core from the hdlcoder_led_blinking/led_counter subsystem, prepare your model by using the configuration parameters, configure your design by using the IP Core editor, and generate the IP core by using the HDL Code tab of the Simulink Toolstrip.

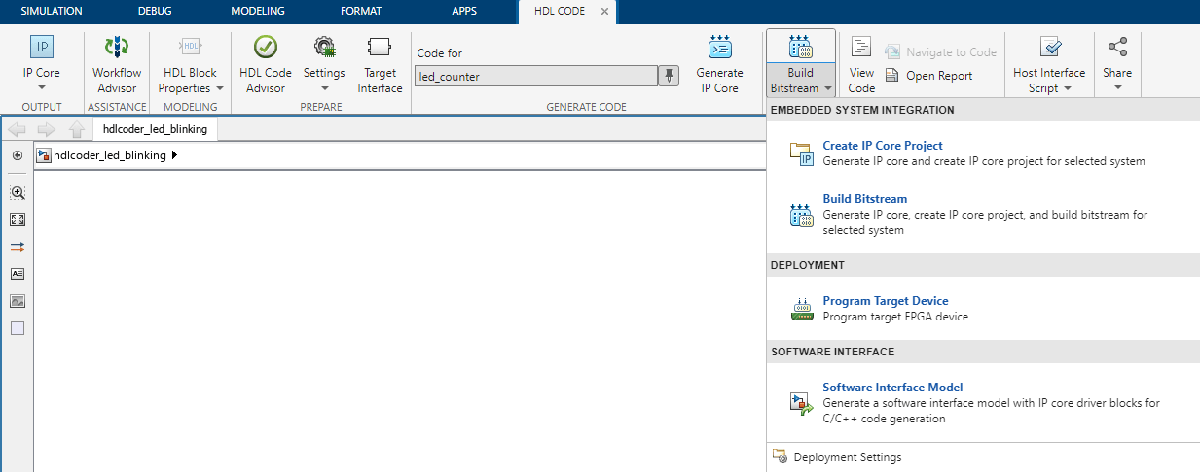

1. In the Apps tab, click HDL Coder. In the HDL Code tab, in the Output section, set the drop-down button to IP Core.

2. Select the led_counter subsystem which is the device under test (DUT) for this example. Make sure that Code for is set to this subsystem. To remember the selection, you can pin this option.

3. Open the HDL Code Generation > Target tab of Configuration Parameters dialog box by clicking the Settings button.

4. Set the Target Platform parameter to Xilinx Zynq ZC702 evaluation kit. If this option does not appear, select Get more to open the Support Package Installer. In the Support Package Installer, select AMD FPGA and SoC Devices and follow the instructions to complete the installation. Ensure the Synthesis Tool is set to Xilinx Vivado.

5. Ensure that the Reference Design parameter is set to Default system.

6. Set the Target Frequency to 50 MHz.

7. Click OK to save your updated settings.

Configure Design and Target Interface

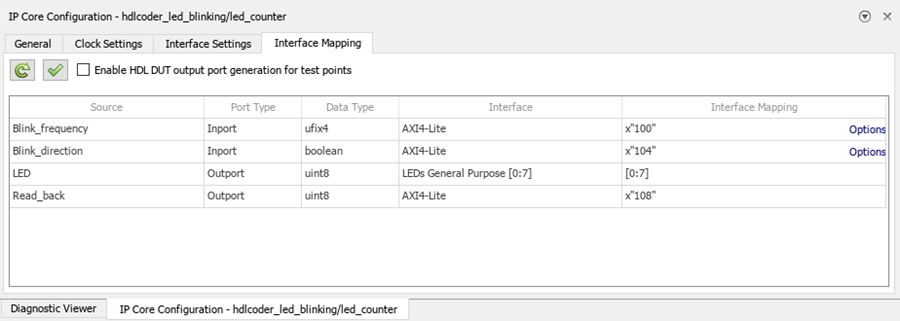

Configure your design to map to the target hardware by mapping the DUT ports to IP core target hardware and setting DUT-level IP core options. In this example, the input ports Blink_frequency and Blink_direction are mapped to the AXI4-Lite interface, so HDL Coder generates AXI interface accessible registers for them. The LED output port is mapped to an external interface, LEDs General Purpose [0:7], which connects to the LED hardware on the Zynq board.

In Simulink, in the HDL Code tab, click Target Interface to open the IP Core editor.

Select the Interface Mapping tab to map each DUT port to one of the IP core target interfaces. The generated design can then communicate with the rest of the hardware system when it is deployed. If no mapping table appears, click the Reload IP core settings

button to compile the model and repopulate the DUT ports and their data types.

button to compile the model and repopulate the DUT ports and their data types.For the DUT ports Blink_frequency, Blink_direction, and Read_back, set the cells in the Interface column to

AXI4-Lite.For the LED output port, set the cell in the Interface column to

LEDs General Purpose [0:7].Validate your settings by clicking the Validate IP core settings

button.

button.

In the IP Core editor, you can optionally adjust the DUT-level IP core settings for your target hardware by:

Using the General tab to configure top-level settings, such as the name of the IP core and whether to generate an IP core report.

Using the Clock Settings tab to configure clock-related settings.

Using the Interface Settings tab to configure interface-related settings, such as the register interface and FPGA data capture properties.

Generate IP Core

After you configure the IP core settings and mappings for your design, you can generate an IP core. In the Simulink Toolstrip, in the HDL Code tab, click Generate IP Core. After you generate the custom IP core, the IP core files are in the ipcore folder in your current directory. To specify a top-level project folder for the ipcore folder to be stored along with all other generated files, in the Configuration Parameters dialog box, use the Project Folder parameter in the HDL Code Generation > Target tab. If the Project Folder parameter is empty, HDL Coder saves the generated files in the current directory.

Generating an IP core also generates the code generation report. In the Code Generation Report window, in the left pane, click the IP Core Generation Report. The report describes the behavior and contents of the generated custom IP core.

Integrate IP Core with Xilinx Vivado Environment

Next, insert your generated IP core into an embedded system reference design by creating a project, generating an FPGA bitstream, and downloading the bitstream to the Zynq hardware.

The reference design is a predefined Xilinx Vivado project that contains all the elements the Xilinx software needs to deploy your design to the Zynq platform, except for the custom IP core and embedded software.

Create IP Core Project

Integrate your generated IP core into the Xilinx platform by creating a Vivado project that organizes and maintains the files associated with the IP core. To create a Vivado project in the Simulink Toolstrip, in the HDL Code tab, select Build Bitstream > Create IP Core Project. HDL Coder generates an IP integrator embedded design and links it in the Diagnostic Viewer.

Configure Deployment Settings

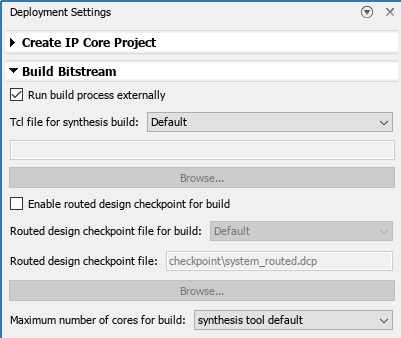

Next, configure the build bitstream settings. In the Simulink Toolstrip in the HDL Code tab**, select Build Bitstream > Deployment Settings**. In the Deployment Settings window under the Build Bitstream section, select Run build process externally to run the Xilinx synthesis tool in a separate window than the current MATLAB session.

In the Deployment Settings window, under the Program Target Device section:

Set Programming method to

Downloadto download the bitstream onto your target Zynq board SD card and load your design when the board power cycles.Set IP Address to your target board IP address.

Set SSH username and SSH Password to your target board settings.

Generate Bitstream and Program Target Device

To generate the bitstream file, in the Simulink Toolstrip, in the HDL Code tab, click Build Bitstream and wait until the synthesis tool runs in the external window.

To download the bitstream, in the Simulink Toolstrip, in the HDL Code tab**,** select Build Bitstream > Program Target Device.

After you program the FPGA hardware, the LED starts blinking on your Zynq board.

Prototype and Verify IP Core on Hardware

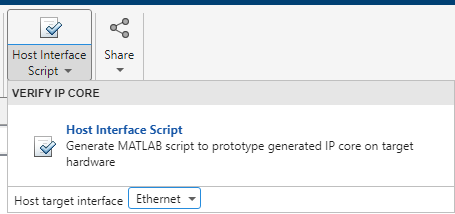

Verify your generated IP core on the hardware by using MATLAB to generate a host interface script. This script contains MATLAB commands that connect your hardware and interact with your IP core. To generate a host interface script file, in the Simulink Toolstrip, in the HDL Code tab, select Host Interface Script > Host Interface Script.

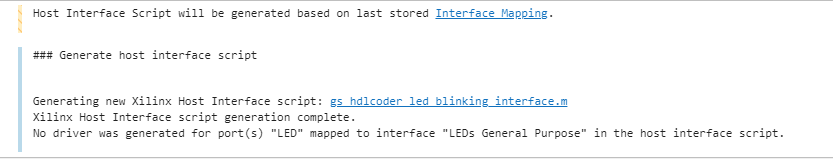

The Simulink Diagnostic Viewer displays a link to the generated host interface script file.

Two MATLAB files are generated in your current folder and enable you to prototype your generated IP core directly from MATLAB.

![]()

Open the generated interface script file by clicking the link in the Simulink Diagnostic Viewer. This file creates a connection to your FPGA hardware that reads and writes data and configures the fpga hardware object with the same ports and interfaces that were mapped in the Target Interface table. This function can be reused in your own scripts to recreate this configuration. For example, uncomment line 33 in the gs_hdlcoder_led_blinking_interface.m function and modify it to change the LED blink frequency. Run the modified script and observe the LED blink frequency changing on the hardware. In addition, uncomment line 35 in the gs_hdlcoder_led_blinking_interface.m function and observe the change in values by reading back the data values.

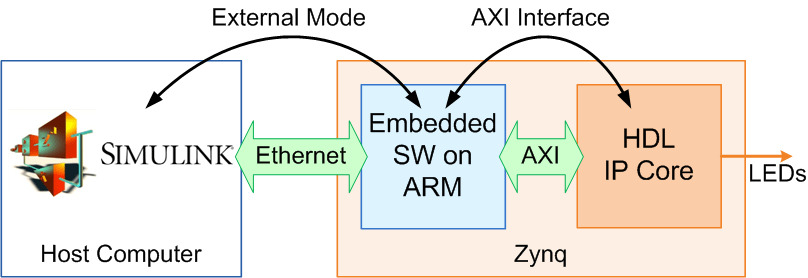

Deploy to Processor Using Software Interface Model

To target a portion of your design for the ARM processor, generate a software interface model. The software interface model contains the part of your design that runs in software. It includes all the blocks outside of the HDL subsystem, and replaces the HDL subsystem with AXI driver blocks. If you have an Embedded Coder license, you can automatically generate embedded code from the software interface model, build it, and run the executable on Linux on the ARM processor. The generated embedded software includes the AXI driver code, generated from the AXI driver blocks, that controls the HDL IP core. You can generate the software interface model at any stage of the IP core generation and IP core integration process.

To generate the software interface model, in the Simulink Toolstrip, in the HDL Code tab, select Build Bitstream > Software Interface Model. The Simulink Diagnostic Viewer displays a link to the generated software interface model.

In the generated software interface model, the led_counter subsystem is replaced with the AXI driver blocks that generate the interface logic between the ARM processor and FPGA.

Run Software Interface Model on Zynq ZC702 Hardware

Next, configure the generated software interface model, generate the embedded C code, and run your model on the ARM processor in the Zynq hardware in external mode.

When you prototype and develop an algorithm, it is useful to monitor and tune the algorithm while it runs on hardware. You can use external mode to deploy your algorithm to the ARM processor in the Zynq hardware, and then link the algorithm with the Simulink model on the host computer through an Ethernet connection.

The Simulink model tunes and monitors the algorithm running on the hardware. Because the ARM processor is connected to the HDL IP core through the AXI interface, you can use external mode to tune parameters, and capture data from the FPGA.

In the generated model,in the Hardware tab, click Hardware settings to open Configuration Parameter dialog box.

In the Solver pane, set Stop time to

inf. Click OK.In the Hardware tab, click Monitor & Tune to run your model on the ARM processor in the Zynq ZC702 hardware in external mode. Embedded Coder builds the model, downloads the ARM executable to the Zynq ZC702 hardware, executes it, and connects the model to the executable.

Double-click the Slider Gain block. Change the slider and observe the change in frequency of the LED array blinking on the Zynq ZC702 hardware. Double-click the Manual Switch block to switch the direction of the blinking LEDs.

Double-click the Scope block connected to the Read_back output port. The Scope block captures the output data of the FPGA IP core.

When you are done changing model parameters, click the Stop button in the toolstrip, then close the system command window.