Multiprocessor Architecture Modeling

Design, evaluate, and implement multiprocessor architecture

modeling

Partition algorithms for multicore execution with inter-processor data communication (IPC) and co-processor (control law accelerator) blocks. With processor-in-the-loop (PIL) simulation, you can cross-compile source code on your development computer, and then download and run the object code on the processor in the hardware board.

Map tasks and peripherals in a model to hardware board configurations using Hardware Mapping tool.

Blocks

Tools

| SoC Builder | Build, load, and execute SoC model on SoC, FPGA, and MCU boards |

| Hardware Mapping | Map tasks and peripherals in a model to hardware board configurations (Since R2022b) |

Topics

Processor-in-Loop (PIL) Simulation

- PIL Simulation

Processor-in-the-Loop (PIL) simulation techniques for Texas Instruments hardware board.

Multiprocessor Modeling

- Use C2000 blocks with Multiprocessor Modeling

Use multiprocessor modeling pass-though block simulation with C2000™ Microcontroller Blockset blocks. - Interprocess Data Communication via Dedicated Hardware Peripheral

Data communication methods between two or more processes within a single processor or across multiple connected processors. - Modeling and Code Generation Using Hardware Interrupt

Model and generate code using Hardware Interrupt block. For multiprocessor modeling use Task Manager block and Hardware Mapping tool. - Streaming Task Profiling

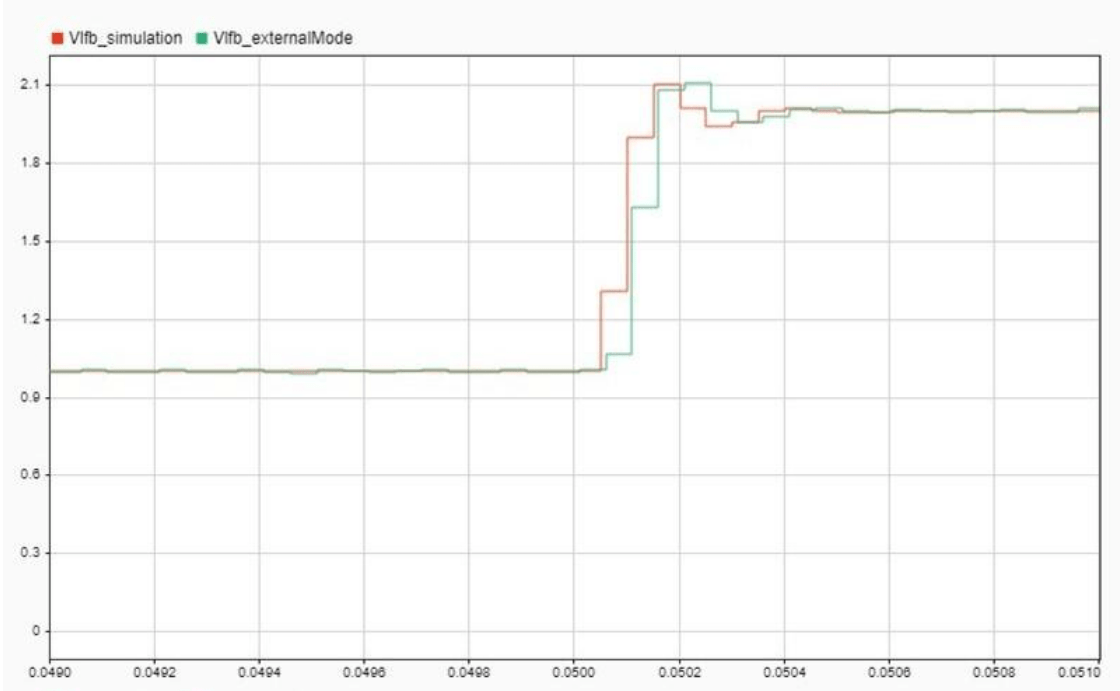

Use the streaming task profiler to measure tasks on the TI C2000 processor. - Run Multiprocessor Models in External Mode

Run a multiprocessor SoC model in external mode running on separate processors on the hardware board. - Modeling Control Law Accelerator (CLA) Using Model Reference

Use the control law accelerator (CLA) co-processor in C2000 MCU models. - Using ARM Cortex-M Coprocessor

Use the ARM® Cortex®-M coprocessor in C2000 MCU models. - Communication Between Cores Using IPC Blocks

Use the IPC blocks to communicate between cores in F2837xD and F2838x processors on the TI C2000 processor.

Troubleshooting

Solve the problems while using SoC Builder for Multiprocessor Architecture Modeling.