Interprocess Data Channel

Model interprocessor data channel between two processors

Libraries:

SoC Blockset /

Processor Interconnect

C2000 Microcontroller Blockset /

Test Bench Blocks

Embedded Coder Support Package for Infineon AURIX TC3x Microcontrollers /

Test Bench Blocks

Embedded Coder Support Package for Infineon AURIX TC4x Microcontrollers /

Test Bench Blocks

Description

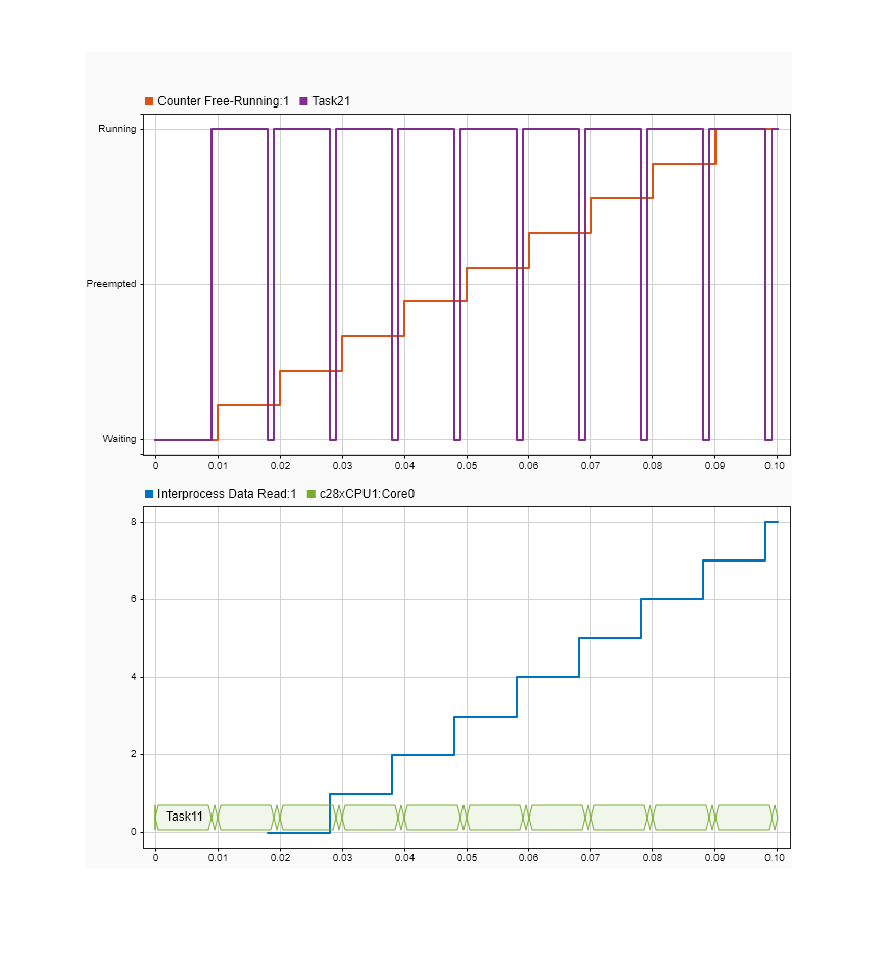

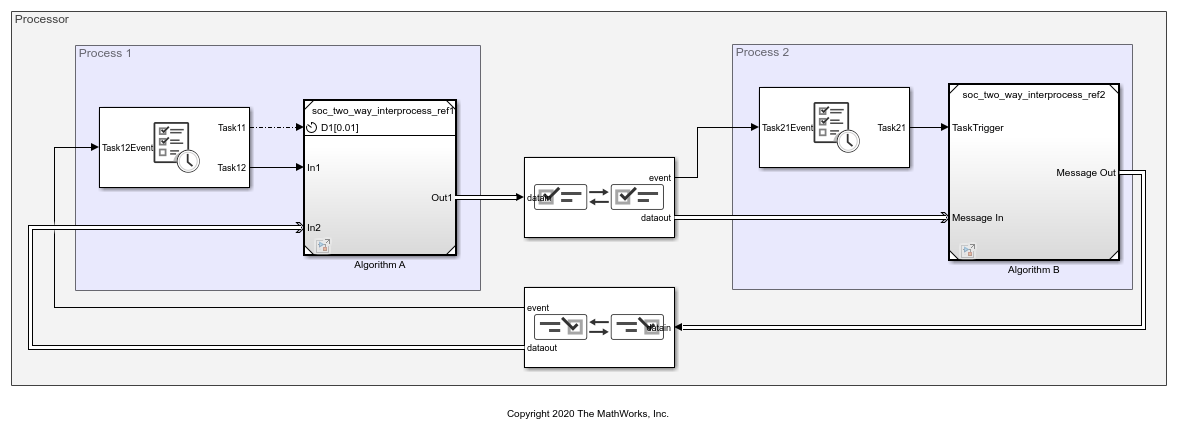

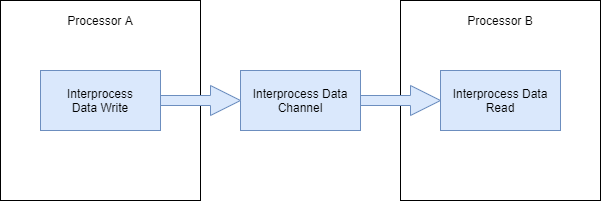

The Interprocess Data Channel block simulates the interprocessor data channel available in multiprocessor or OS managed SoC hardware board families. The block provides a channel for asynchronous data transfer between two processors. This diagram shows a generalized view of the interprocessor data connection.

Note

If you are using multiprocessor modeling approach with single model triggering multiple cores using Task manager, use the Interprocess Data Read and Interprocess Data Write blocks to send and receive data between cores.

Use IPC Receive and IPC Transmit blocks to receive or sent data to either core for multi-core processors. Use these blocks for flat model approach where you are using separate models for each core.

To help you choose the right solution for your application, see Communication Between Cores Using IPC Blocks for the detailed comparison between the IPC Transmit/Receive blocks and Interprocess Data Read/Write blocks.

Examples

Limitations

In an SoC model, when Interprocess Data Channel blocks form a closed-loop between two or more tasks, it can create an artificial algebraic loop for the Simulink® solver. To break the loop, the Simulink solver implicitly adds a delay into the loop. This delay is related to an internal event and cannot be modified by the user, but the delay typically will be on the same order as the base time-step of the model. For more information on artificial algebraic loops in Simulink solvers, see Artificial Algebraic Loops.

Ports

Input

Output

Parameters

Version History

Introduced in R2020b