Interprocess Data Write

Send messages to another processor using interprocessor data write

Libraries:

SoC Blockset /

Processor Interconnect

C2000 Microcontroller Blockset /

Target Communication

Embedded Coder Support Package for Infineon AURIX TC3x Microcontrollers /

Target Communication

Embedded Coder Support Package for Infineon AURIX TC4x Microcontrollers /

Target Communication

Description

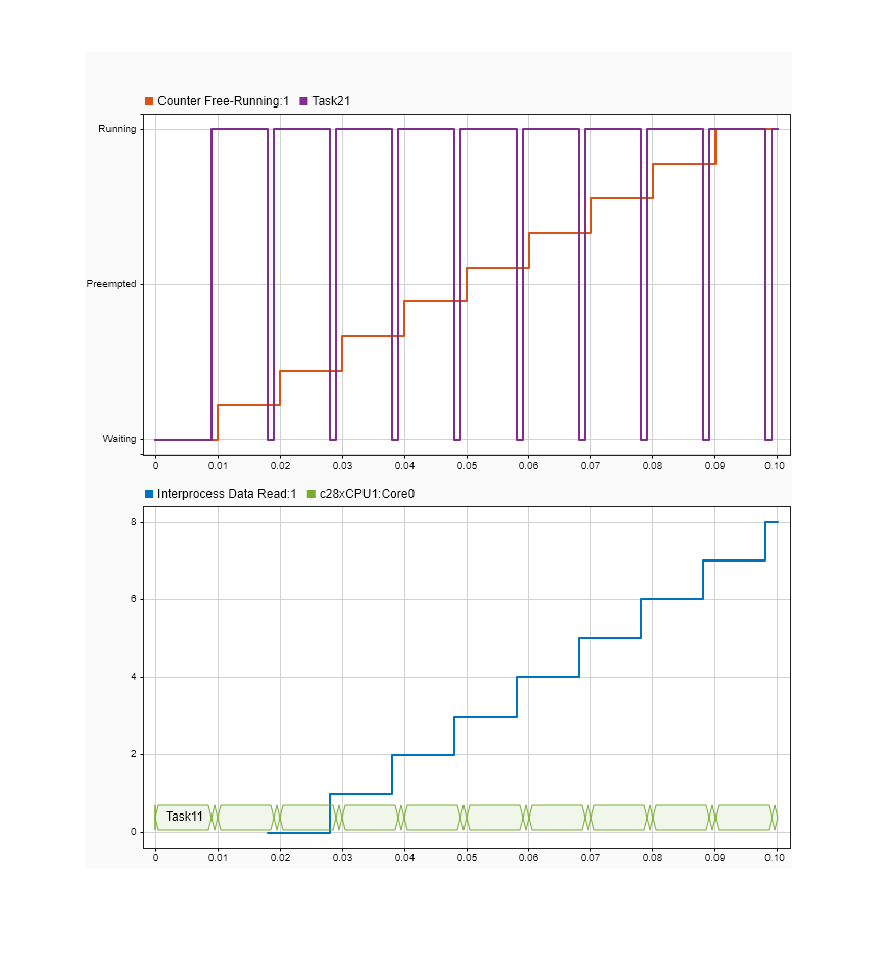

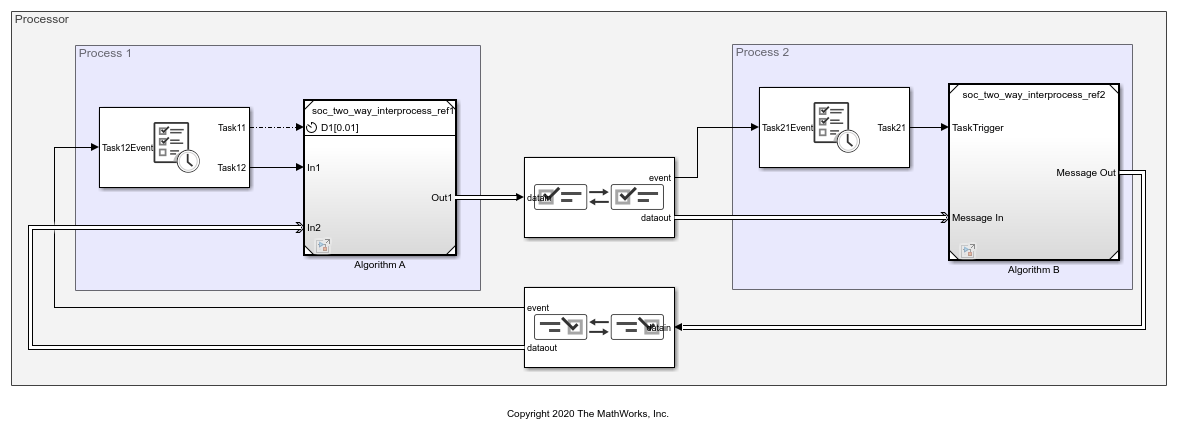

The Interprocess Data Write block asynchronously sends messages to another processor in an SoC using an interprocess data channel. The Interprocess Data Write block connects to an Interprocess Data Channel block that similarly connects to an Interprocess Data Read block contained in a separate processor reference model. In simulation, data from the current processor is asynchronously sent and processed in the processor containing the Interprocess Data Read block and associated asynchronous task. This diagram shows a generalized view of the interprocess data channel.

Note

Ensure that the number of buffers specified must same at both the Tx and Rx side.

If you are using multiprocessor modeling approach with single model triggering multiple cores using Task manager, use the Interprocess Data Read and Interprocess Data Write blocks to send and receive data between cores.

Examples

Ports

Input

Output

Parameters

Version History

Introduced in R2020b