HDL Identifiers and Comments

Specifying a Header Comment

The coder includes a header comment block at the top of the files it generates. The header comment block contains the specifications of the generating filter and the coder options that were selected at the time HDL code was generated.

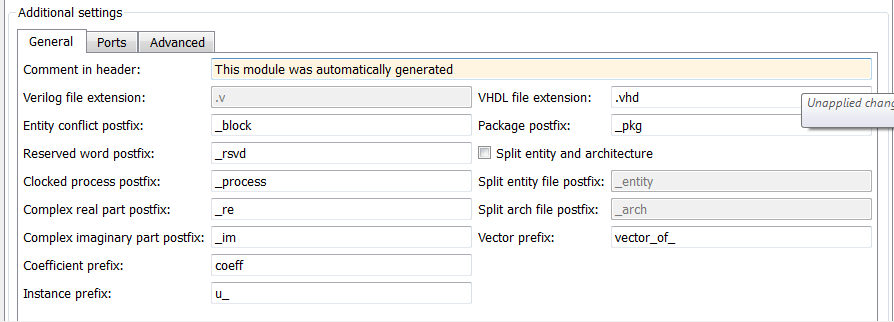

You can use the Comment in header option to add a comment to the

end of the header comment block in each generated file. For example, use this option to add

“This module was automatically generated”. With this

change, the preceding header comment block would appear as follows:

-- ------------------------------------------------------------- -- -- Module: Hlp -- -- Generated by MATLAB(R) 7.11 and the Filter Design HDL Coder 2.7. -- -- Generated on: 2010-08-31 13:32:16 -- -- This module was automatically generated -- -- ------------------------------------------------------------- -- ------------------------------------------------------------- -- HDL Code Generation Options: -- -- TargetLanguage: VHDL -- Name: Hlp -- UserComment: User data, length 47 -- Filter Specifications: -- -- Sampling Frequency : N/A (normalized frequency) -- Response : Lowpass -- Specification : Fp,Fst,Ap,Ast -- Passband Edge : 0.45 -- Stopband Edge : 0.55 -- Passband Ripple : 1 dB -- Stopband Atten. : 60 dB -- ------------------------------------------------------------- -- ------------------------------------------------------------- -- HDL Implementation : Fully parallel -- Multipliers : 43 -- Folding Factor : 1 -- ------------------------------------------------------------- -- Filter Settings: -- -- Discrete-Time FIR Filter (real) -- ------------------------------- -- Filter Structure : Direct-Form FIR -- Filter Length : 43 -- Stable : Yes -- Linear Phase : Yes (Type 1) -- Arithmetic : fixed -- Numerator : s16,16 -> [-5.000000e-001 5.000000e-001) -- Input : s16,15 -> [-1 1) -- Filter Internals : Full Precision -- Output : s33,31 -> [-2 2) (auto determined) -- Product : s31,31 -> [-5.000000e-001 5.000000e-001) (auto determined) -- Accumulator : s33,31 -> [-2 2) (auto determined) -- Round Mode : No rounding -- Overflow Mode : No overflow -- -------------------------------------------------------------

To add a header comment,

Select the Global Settings tab on the Generate HDL tool.

Select the General tab in the Additional settings pane.

Type the comment text in the Comment in header field, as shown in this figure.

Command-Line Alternative: Use the generatehdl function with the property UserComment to add a comment to

the end of the header comment block in each generated HDL file.

Resolving Entity or Module Name Conflicts

The coder checks whether multiple entities in VHDL® or multiple modules in Verilog® share the same name. If a name conflict exists, the coder appends the postfix

'_block' to the second of the two matching character vectors.

To change the postfix:

Select the Global Settings tab on the Generate HDL tool.

Select the General tab in the Additional settings pane.

Enter a new character vector in the Entity conflict postfix field, as shown in this figure.

Command-Line Alternative: Use the generatehdl function with the property EntityConflictPostfix

to change the entity or module conflict postfix.

Resolving HDL Reserved Word Conflicts

The coder checks whether character vectors that you specify as names, postfix values, or labels are VHDL or Verilog reserved words. See Reserved Word Tables for listings of VHDL and Verilog reserved words.

If you specify a reserved word, the coder appends the postfix _rsvd

to the character vector. For example, if you try to name your filter mod,

for VHDL code, the coder adds the postfix _rsvd to form the name

mod_rsvd.

To change the postfix:

Select the Global Settings tab on the Generate HDL tool.

Select the General tab in the Additional settings pane.

Enter a new character vector in the Reserved word postfix field, as shown in this figure.

Command-Line Alternative: Use the generatehdl function with the property ReservedWordPostfix to

change the reserved word postfix.

Reserved Word Tables

The tables list VHDL and Verilog reserved words.

VHDL Reserved Words

abs | access | after | alias | all |

and | architecture | array | assert | attribute |

begin | block | body | buffer | bus |

case | component | configuration | constant | disconnect |

downto | else | elsif | end | entity |

exit | file | for | function | generate |

generic | group | guarded | if | impure |

in | inertial | inout | is | label |

library | linkage | literal | loop | map |

mod | nand | new | next | nor |

not | null | of | on | open |

or | others | out | package | port |

postponed | procedure | process | pure | range |

record | register | reject | rem | report |

return | rol | ror | select | severity |

signal | shared | sla | sll | sra |

srl | subtype | then | to | transport |

type | unaffected | units | until | use |

variable | wait | when | while | with |

xnor | xor |

Verilog Reserved Words

always | and | assign | automatic | begin |

buf | bufif0 | bufif1 | case | casex |

casez | cell | cmos | config | deassign |

default | defparam | design | disable | edge |

else | end | endcase | endconfig | endfunction |

endgenerate | endmodule | endprimitive | endspecify | endtable |

endtask | event | for | force | forever |

fork | function | generate | genvar | highz0 |

highz1 | if | ifnone | incdir | include |

initial | inout | input | instance | integer |

join | large | liblist | library | localparam |

macromodule | medium | module | nand | negedge |

nmos | nor | noshowcancelled | not | notif0 |

notif1 | or | output | parameter | pmos |

posedge | primitive | pull0 | pull1 | pulldown |

pullup | pulsestyle_onevent | pulsestyle_ondetect | rcmos | real |

realtime | reg | release | repeat | rnmos |

rpmos | rtran | rtranif0 | rtranif1 | scalared |

showcancelled | signed | small | specify | specparam |

strong0 | strong1 | supply0 | supply1 | table |

task | time | tran | tranif0 | tranif1 |

tri | tri0 | tri1 | triand | trior |

trireg | unsigned | use | vectored | wait |

wand | weak0 | weak1 | while | wire |

wor | xnor | xor |

Setting the Postfix for VHDL Package Files

By default, the coder appends the postfix _pkg to the base file name

when generating a VHDL package file. To rename the postfix for package files, do these steps.

Select the Global Settings tab on the Generate HDL tool.

Select the General tab in the Additional settings pane.

Specify a new value in the Package postfix field.

Note

When specifying a character vector for use as a postfix in file names, consider the size of the base name and platform-specific file naming requirements and restrictions.

Command-Line Alternative: Use the generatehdl function with the PackagePostfix property to

rename the file name postfix for VHDL package files.

Specifying a Prefix for Filter Coefficients

The coder declares the coefficients for the filter as constants within a

rtl architecture. The coder derives the constant names adding the

prefix coeff. The coefficient names depend on the type of filter.

| For... | The Prefix Is Concatenated with... |

|---|---|

| FIR filters | Each coefficient number, starting with 1. Examples:

|

| IIR filters | An underscore (_) and an Example:

|

For example:

ARCHITECTURE rtl OF filt IS -- Type Definitions TYPE delay_pipeline_type IS ARRAY(NATURAL range <>) OF signed(15 DOWNTO 0);-- sfix16_En15 CONSTANT coeff1 : signed(15 DOWNTO 0) := to_signed(-30, 16); -- sfix16_En15 CONSTANT coeff2 : signed(15 DOWNTO 0) := to_signed(-89, 16); -- sfix16_En15 CONSTANT coeff3 : signed(15 DOWNTO 0) := to_signed(-81, 16); -- sfix16_En15 CONSTANT coeff4 : signed(15 DOWNTO 0) := to_signed(120, 16); -- sfix16_En15

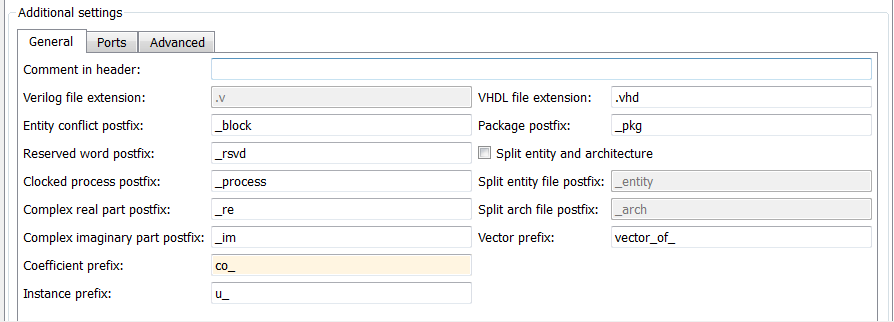

To use a prefix other than coeff,

Select the Global Settings tab on the Generate HDL tool.

Select the General tab in the Additional settings pane.

Enter a new character vector in the Coefficient prefix field, as shown in this figure.

The character vector that you specify

Must start with a letter.

Cannot include a double underscore (__).

Note

If you specify a VHDL or Verilog reserved word, the coder appends a reserved word postfix to the character vector to form a valid identifier. If you specify a prefix that ends with an underscore, the coder replaces the underscore character with

under. For example, if you specifycoef_, the coder generates coefficient names such ascoefunder1.

Command-Line Alternative: Use the generatehdl function with the property CoeffPrefix to change the base

name for filter coefficients.

Specifying a Postfix for Process Block Labels

The coder generates process blocks to modify the content of the registers. The label

for each of these blocks is derived from a register name and the postfix

_process. For example, the coder derives the label

delay_pipeline_process in the following block from the register name

delay_pipeline and the postfix '_process'.

delay_pipeline_process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

delay_pipeline (0 To 50) <= (OTHERS => (OTHERS => '0'));

ELSIF clk'event AND clk = '1' THEN

IF clk_enable = '1' THEN

delay_pipeline(0) <= signed(filter_in)

delay_pipeline(1 TO 50) <= delay_pipeline(0 TO 49);

END IF;

END IF;

END PROCESS delay_pipeline_process;

The Clocked process postfix property lets you change the postfix to

a value other than '_process'. For example, to change the postfix to

'_clkproc', do these steps.

Select the Global Settings tab on the Generate HDL tool.

Select the General tab in the Additional settings pane.

Enter a new character vector in the Clocked process postfix field, as shown in this figure.

Command-Line Alternative: Use the generatehdl function with the property ClockProcessPostfix to

change the postfix appended to process labels.

Setting a Prefix for Component Instance Names

Instance prefix specifies a character vector to be prefixed to

component instance names in generated code. The default is 'u_'.

You can set the prefix to a value other than 'u_'. To change the

prefix:

Select the Global Settings tab on the Generate HDL tool.

Select the General tab in the Additional settings pane.

Enter a new character vector in the Instance prefix field, as shown in this figure.

Command-Line Alternative: Use the generatehdl function with the property InstancePrefix to change the

instance prefix.

Setting a Prefix for Vector Names

Vector prefix specifies a character vector to be prefixed to vector

names in generated VHDL code. The default is 'vector_of_'.

Note

Vector prefix is not supported for Verilog code generation.

You can set the prefix to a value other than 'vector_of_'. To change

the prefix:

Select the Global Settings tab on the Generate HDL tool.

Select the General tab in the Additional settings pane.

Enter a new character vector in the Vector prefix field, as shown in this figure.

Command-Line Alternative: Use the generatehdl function with the property VectorPrefix to change the

instance prefix.