Improve FPGA Sampling Frequency of HDL Implementation Model Generated from Simscape Algorithm

If you design your algorithm by using Simscape™ blocks, you can run the Simscape HDL Workflow Advisor to generate an HDL implementation model. When you open the HDL implementation model, you see the HDL algorithm that models the state-space representation by using Simulink® blocks that are compatible for HDL code generation. To learn more about the Simscape HDL Workflow Advisor, see Simscape HDL Workflow Advisor Tasks.

FPGA Sampling Frequency

FPGA sampling frequency is the frequency at which the models run on the hardware. When you generate HDL code and deploy the plant model onto an FPGA, you may want to improve the FPGA sampling frequency. The FPGA sampling frequency depends on these parameters:

FPGA clock frequency

Oversampling factor

Number of solver iterations

![]()

FPGA sample time is the sample time at which the models run on the hardware. It is reciprocal of the FPGA sampling frequency.

![]()

To improve the FPGA sampling frequency, you can find a tradeoff between improving the FPGA clock frequency, and balancing the oversampling factor and number of solver iterations. To learn more about how these parameters affect FPGA sampling frequency, see Troubleshooting Real-Time Hardware Deployment Issues in Simscape Hardware-in-the-Loop Workflow.

Simscape sampling frequency is the reciprocal of the Simscape sample time. In the Solver Configuration (Simscape) block dialog box, you can specify the value of Simscape sample time in the Sample time parameter text box under the Use local solver option.

Note

To get accurate results on hardware, ensure that the Simscape sample time matches the FPGA sample time. For Simscape models containing a single Simscape network, the Simscape HDL Workflow Advisor calculates the target frequency to run the model on the hardware and automatically handles the oversampling factor. However, if the desired sample time is not achievable, then the Advisor displays a warning message providing details of estimated achievable frequency. To learn more, see Estimate Achievable Target Frequency Without Running Synthesis.

The preceding section uses the boost converter model as an example to illustrate how you can modify the oversampling factor and the number of solver iterations to improve the FPGA sample time.

Boost Converter Model

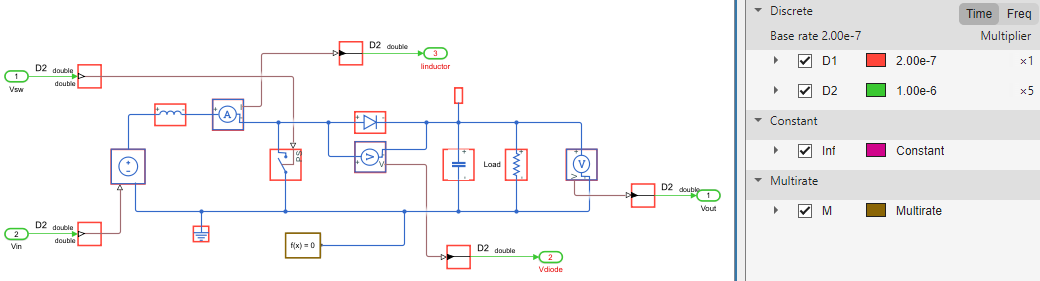

This example uses the boost converter model to illustrate the change in Simscape sample time in the generated HDL implementation model and the oversampling factor that is saved on the model.

Open the boost converter model. To learn how the boost converter is implemented, open the

Simscape_systemSubsystem. To open the boost converter model, in the MATLAB® Command Window, enter:openExample('plantdeployment/OpenTheSimscapeHDLWorkflowAdvisorExample',... 'supportingFile','sschdlexBoostConverterExample') open_system('sschdlexBoostConverterExample/Simscape_system')

You see that the Simscape sample time for the model is

1e-6. The sample time of2.00e-7corresponds to the sample time of the sources that drive the Simscape algorithm.Open the Simscape HDL Workflow Advisor for your model:

sschdladvisor('sschdlexBoostConverterExample')Run the workflow to the Generate implementation model task.

After running this task, you see a link to the generated HDL implementation model. Click the link to open the HDL implementation model.

Simulate the HDL implementation model. When you navigate the model to the

HDL AlgorithmSubsystem, you see that the model usessingledata types and runs at a sample time5.00e-7, which is5times faster than the original Simscape model.

Run this command to see the HDL parameter settings that are saved on the model:

hdlsaveparams('gmStateSpaceHDL_sschdlexBoostConverterExamp')%% Set Model 'gmStateSpaceHDL_sschdlexBoostConverterExamp' HDL parameters hdlset_param('gmStateSpaceHDL_sschdlexBoostConverterExamp', 'AutoRoute', 'off'); hdlset_param('gmStateSpaceHDL_sschdlexBoostConverterExamp', 'FPToleranceValue', 1.000000e-03); fpconfig = hdlcoder.createFloatingPointTargetConfig('NATIVEFLOATINGPOINT' ... , 'LatencyStrategy', 'Min' ... ); hdlset_param('gmStateSpaceHDL_sschdlexBoostConverterExamp', 'FloatingPointTargetConfiguration', fpconfig); hdlset_param('gmStateSpaceHDL_sschdlexBoostConverterExamp', 'HDLSubsystem',... 'gmStateSpaceHDL_sschdlexBoostConverterExamp/Simscape_system/HDL Subsystem'); hdlset_param('gmStateSpaceHDL_sschdlexBoostConverterExamp', 'MaskParameterAsGeneric', 'on'); hdlset_param('gmStateSpaceHDL_sschdlexBoostConverterExamp', 'Oversampling', 55); hdlset_param('gmStateSpaceHDL_sschdlexBoostConverterExamp', 'UseFloatingPoint', 'on'); hdlset_param('gmStateSpaceHDL_sschdlexBoostConverterExamp/Simscape_system/HDL Subsystem/HDL Algorithm... /Mode Selection/Generate Mode Vector', 'Architecture', 'MATLAB Datapath');

The HDL parameters that are saved indicate that the model has the native floating-point

mode enabled and uses an Oversampling factor of 55

and has Latency Strategy set to MIN. These default

values chosen for number of solver iterations and combination of HDL parameters offer an

optimal tradeoff between oversampling factor and the target FPGA clock frequency and

improves the FPGA sampling frequency. To further improve the FPGA sampling frequency, you

can reduce the number of iterations and the oversampling factor as per the description here.

Based on the suggested changes, you can verify if your model is compatible for these

modifications.

Reducing Number of Solver Iterations

For each mode in the physical system, the workflow generates a state-space representation. The solver method is iterative and performs multiple computations to determine the correct mode for the next time step. After a certain number of iterations, the output value from the next time step becomes the same as the value from the previous time step. This consistency in the output value indicates the correct number of solver iterations.

The Advisor by default chooses an optimal value for the number of solver iterations. See Using Number of Solver Iterations. To improve the FPGA sampling frequency, reduce the number of solver iterations. The number of solver iterations depends on various factors such as the complexity of your design, the number of modes in the design that the workflow calculates, and so on.

In the Solver Configuration (Simscape) block, select the

Use fixed-cost runtime consistency iterations check box and specify a

custom value for the number of solver iterations in Nonlinear

iterations text box. Start by reducing the number of solver iterations to a

value such as 3.

In the Generate implementation model task of the Simscape HDL Workflow Advisor, select Generate validation logic for the implementation model, and then generate the HDL implementation model. Simulate the HDL implementation model and open the Diagnostic Viewer to verify that the model does not display warnings or assertions.

If you see warnings or assertions, it indicates a simulation mismatch because the number

of solver iterations that you specified is not adequate to compute the required number of

modes in the state-space design. Resolve the mismatch by increasing the validation logic

tolerance value or the number of solver iterations. Changing Floating-point

precision to double is not recommended. Double-precision

operations have large latencies and require a large Oversampling factor

to allocate sufficient delays, which reduces the sampling frequency. See Validate HDL Implementation Model to Simscape Algorithm.

Using Oversampling Factor and Latency Strategy

The Oversampling factor specifies the factor by which the FPGA clock rate is a multiple of the HDL implementation model base sample rate. The HDL implementation model contains feedback loops and performs multiplication of large matrices that have floating-point data types inside the feedback loops. To accommodate the large latency introduced by these floating-point operations inside the feedback loops, the code generator uses a large value of oversampling factor in conjunction with the clock-rate pipelining optimization on the model. For more information, see Generate a Global Oversampling Clock.

You vary the oversampling factor and latency strategy of the floating-point operator in

conjunction. The default oversampling factor of 55 and minimum latency

strategy gives an optimal sampling frequency. To achieve the maximum FPGA clock frequency,

use the maximum latency strategy. When you specify this latency strategy, the floating-point

operations introduce the maximum number of delays and higher FPGA clock frequency is

achievable. To allocate these delays, increase the oversampling factor. If the increase in

FPGA clock frequency outweighs the increase in oversampling factor, you achieve a higher

sampling frequency.

To change the latency strategy and oversampling factor in conjunction from the Configuration Parameters dialog box:

On the HDL Code Generation > Floating Point pane, change the Latency Strategy to

Max.On the HDL Code Generation > Global Settings pane, increase the Oversampling factor to a value such as

100depending on the complexity of your HDL design.

For the boost converter model, the default settings of Number of solver

iterations set to 5, Oversampling

factor set to 55, and Latency Strategy

set to Min provides the optimal FPGA sampling frequency.

See Also

Functions

sschdladvisor|simscape.findNonlinearBlocks(Simscape)

Topics

- Solvers for Real-Time Simulation (Simscape)

- Simscape HDL Workflow Advisor Best Practices

- Latency Considerations with Native Floating Point

- Generate Simulink Real-Time Interface Subsystem for Simscape Two-Level Converter Model

- Troubleshooting Real-Time Hardware Deployment Issues in Simscape Hardware-in-the-Loop Workflow

- Troubleshoot Validation Errors in Simscape Hardware-in-the-Loop Workflow