Prototype Generated IP Core on Hardware using FPGA I/O

This example shows how to use MATLAB® to prototype an algorithm running on FPGA hardware from your host computer. The example demonstrates the workflow on the Versal AI Core Series VCK190 Evaluation Kit, but can be run on any Xilinx® Zynq®, UltraScale+™, or Versal® board supported by HDL Coder.

Introduction

At many stages in the design process it can be useful to interact with an FPGA design that is running directly on hardware. Working with hardware enables you to rapidly prototype designs, verify functionality, tune key parameters, connect to real-world signals, collect data for analysis, and much more.

This example shows you how to connect MATLAB on your host computer to your FPGA hardware. Use MATLAB to:

Write input signals to your FPGA algorithm.

Capture output signals from your FPGA for analysis.

Read from and write to registers in your FPGA design.

As part of this example, you:

Generate and deploy a simple algorithm on hardware.

Create a hardware object to establish a connection to your FPGA.

Use a simple script to prototype the design running on hardware with live data.

Before You Begin

To run this example, install and set up:

HDL Coder™ Support Package for AMD® FPGA and SoC Devices

Xilinx Vivado® (version indicated in HDL Language Support and Supported Third-Party Tools and Hardware)

Any Xilinx SoC board supported by HDL Coder. This example uses the Versal AI Core Series VCK190 Evaluation Kit.

To setup the Versal, see Set Up Xilinx Versal ACAP Hardware and Tools in Getting Started with Targeting Xilinx Versal Adaptive SoC Platform.

MathWorks® firmware image on the board’s SD card. For help with SD card setup, see Guided Hardware Setup for AMD Boards (HDL Coder Support Package for AMD FPGA and SoC Devices).

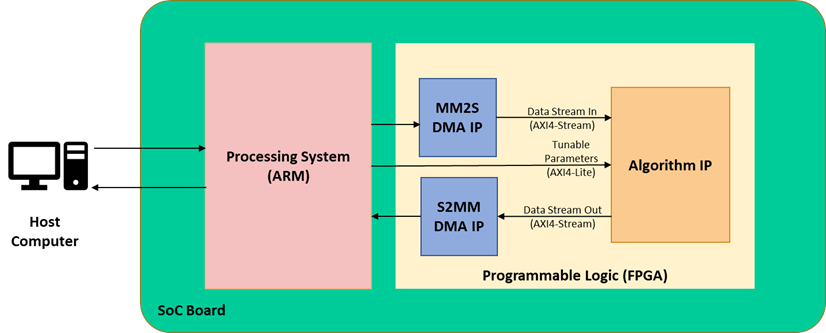

System Architecture

The preceding image shows the high-level architecture of the system. The host computer communicates to the FPGA through the processing system on the System on Chip (SoC) board. The host computer can send and receive frames of data, which are translated to and from streaming data by the Direct Memory Access (DMA) IPs. The host computer can also tune parameters by writing to AXI4-Lite registers within the algorithm IP core.

FPGA Algorithm

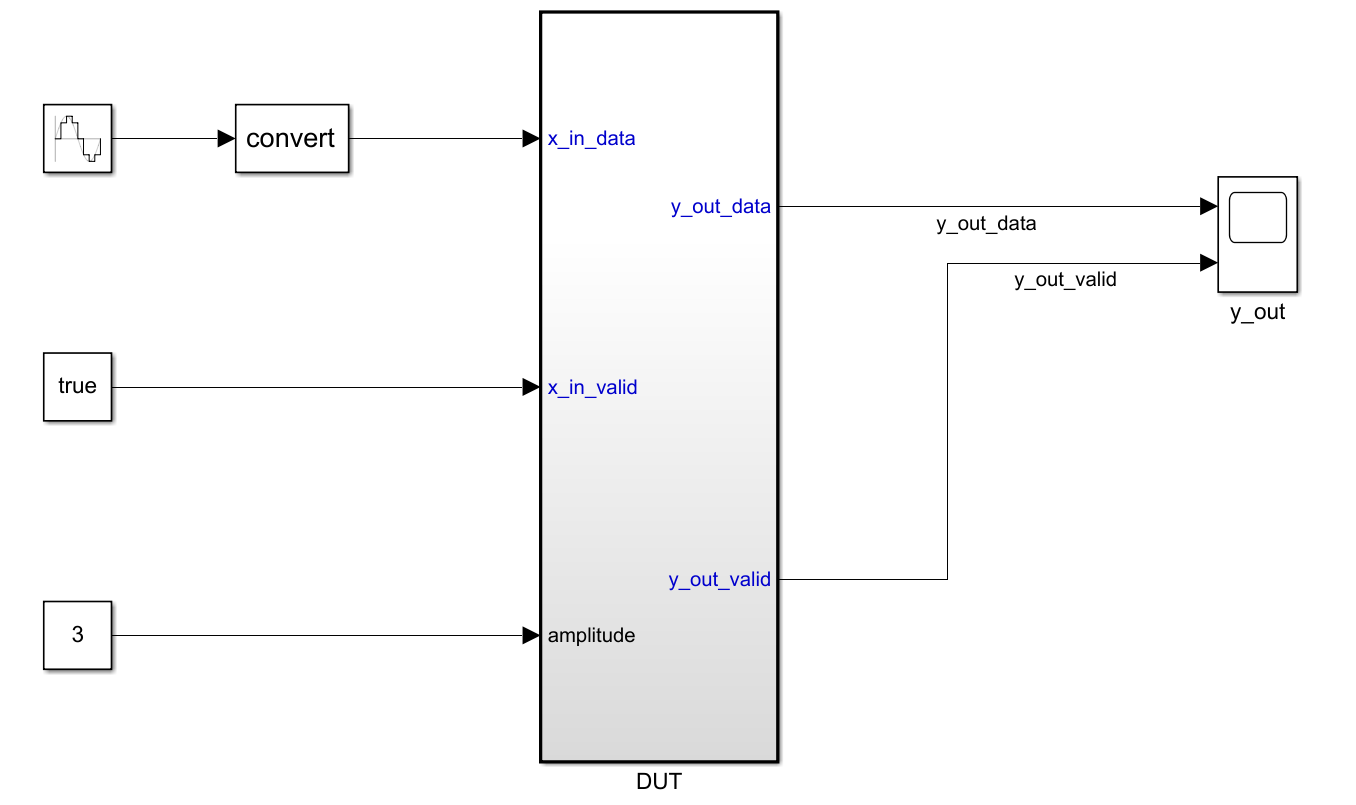

The algorithm deployed to the FPGA is a simple streaming algorithm that scales the amplitude of the input signal by a constant. The streaming data is modeled with data and valid signals. The amplitude signal is modeled as a constant.

Open the model. The model consists of the design under test (DUT) and the testbench. The DUT contains the algorithm that is deployed to the FPGA. The testbench exercises the DUT during simulation by providing inputs and capturing outputs for display.

open_system hdlcoder_scale_amplitude.slx

Generate HDL IP Core

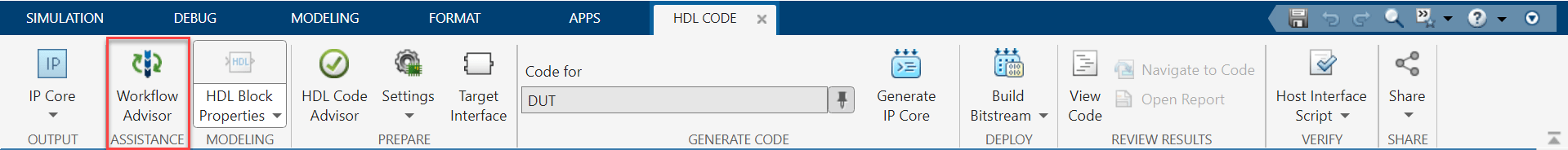

To generate an IP core from the DUT by using the HDL Workflow Advisor:

1. Set up the Xilinx Vivado synthesis tool path using the following command in the MATLAB Command Window. Use your own Vivado installation path when you run the command.

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','C:\Xilinx\Vivado\2020.2\bin\vivado.bat');

2. Open the HDL Coder toolstrip app from Apps > HDL Coder. Click the toolstrip icon to open the Workflow Advisor.

3. In the Set Target Device and Synthesis Tool task, select IP Core Generation for Target workflow and Xilinx Versal AI Core Series VCK190 Evaluation Kit for Target platform. If you are targeting a different Xilinx SoC, choose your board from the Target platform context menu.

Click Run This Task.

4. In the Set Target Reference Design task, select Default system with AXI4-Stream interface for Reference design.

Click Run This Task.

5. In Set Target Interface task, the ports of the DUT subsystem are mapped to IP Core interfaces. The input data and valid ports are mapped to AXI4-Stream Slave. The output data and valid ports are mapped to AXI4-Stream Master. The amplitude signal is mapped to AXI4-Lite.

Click Run This Task.

6) Right-click the Generate RTL Code and IP Core task, and select Run to Selected Task to generate the IP core.

Generate Interface Between Host Computer and IP Core

To generate a host computer interface to the IP core and deploy the design to the target hardware board:

1. Run the Create Project task. This task inserts the generated IP core for the FPGA algorithm into the reference design to create the system shown in the System Architecture diagram.

2. In the Generate Software Interface task, select the box for Generate host interface script then run this task.

3. Two MATLAB files are generated in your current folder that enable you to prototype your generated IP core directly from MATLAB.

4. Inspect these generated files in Interact with FPGA Design from Host Computer. First, complete the remaining Workflow Advisor tasks. Run the Build FPGA Bitstream task, which might take some time to finish.

5. Run the Program Target Device task to program the FPGA algorithm onto the board. Choose the Download programming method, which downloads the FPGA bitstream onto the SD card and configures the ARM processing system to start up properly.

Interact with FPGA Design from Host Computer

Interact with the FPGA design by reading and writing data from MATLAB on the host computer.

Open the generated script file:

open gs_hdlcoder_scale_amplitude_interface.m

This file creates a connection to your FPGA hardware for reading and writing data.

Creates a Processor hardware object, which represents a connection from MATLAB to the processor on your Xilinx SoC board.

Creates an “fpga” hardware object, which represents a connection to the FPGA through the processor on your hardware board.

Configures the “fpga” object with the desired hardware interfaces and ports from your DUT algorithm.

Reads and writes data to DUT ports to exercise your algorithm running on hardware.

Releases any hardware resources used by the

fpgaobject to clean up the connection.

Open the generated setup function:

open gs_hdlcoder_scale_amplitude_setup.m

This function configures the fpga hardware object with the same ports and interfaces that were mapped in the Set Target Interface task. You can reuse this function can be reused in your own scripts to recreate this configuration.

You can modify the generated script file to exercise the algorithm running on hardware. A live script has been prepared, which you can open by running this command:

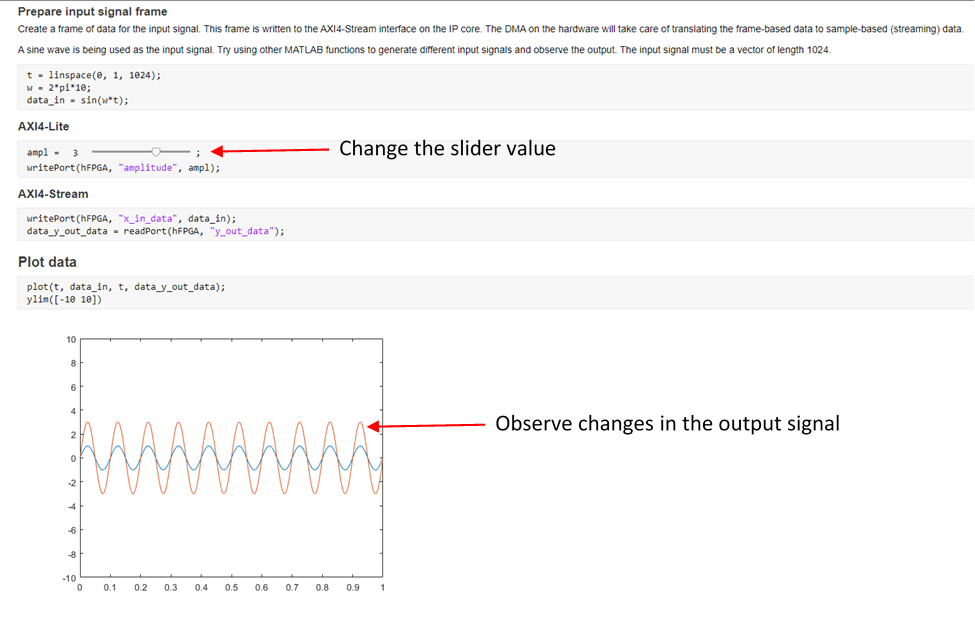

open hdlcoder_scale_amplitude_script.mlxChange the slider value and observe how the output data (orange) changes in the graph below it. As the slider moves, the code below it is executed. Each execution of the code:

Writes the new amplitude value from the slider to an AXI register in the IP core.

Writes one frame of the input signal.

Reads one frame of output signal.

Plots the input and output signals on the same graph to show the difference in amplitude.

When finished, run the last line of the script to release any hardware resources used by the fpga object for clean up:

release(hFPGA);

Next Steps

Experiment further with the generated script:

Change the MATLAB function used to produce the input signal data on the line 7 of the live script. Some other functions to try are

cos,square(Signal Processing Toolbox), andsawtooth(Signal Processing Toolbox).Use Develop Apps Using App Designer to create a custom app with the commands from this script. Add User Interface (UI) components for interacting with the algorithm as it runs on the hardware.

Follow the steps from this example with your own model. Use the generated script to prototype your algorithm on hardware.