Generate IP Core from Multirate Model

This example shows HDL Coder™ supports designs with multiple sample rates when you run the IP Core Generation workflow.

If you are only using register interfaces such as AXI4 or AXI4-Lite, and when you use Free running for Processor/FPGA Synchronization, you can use multiple sample rates in your design without restrictions.

When you map the interface ports to AXI4-Stream Video, or AXI4 Master interfaces, to use multiple sample rates, make sure that the DUT ports that map to the AXI4 interfaces run at the fastest rate of the design after HDL code generation.

These examples illustrate how you can model your design with multiple sample rates when using AXI4-Stream, AXI4-Stream Video, or AXI4-Master Master interfaces.

Run Part of Design at Slower Rate

You can run part of the design at a slower rate while making sure that the DUT ports that map to the interface run at the fastest rate. This example illustrates mapping to AXI4-Stream Video interfaces but you can map to AXI4-Stream or AXI4 Master interfaces by using this approach.

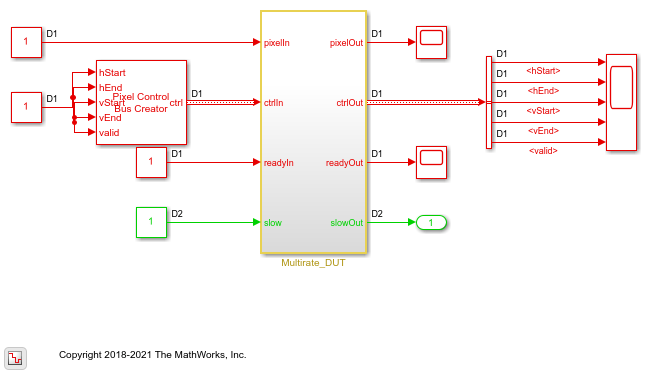

For an example, open the model hdlcoder_axi_video_multirate.

load_system('hdlcoder_axi_video_multirate') set_param('hdlcoder_axi_video_multirate','SimulationCommand','update') open_system('hdlcoder_axi_video_multirate')

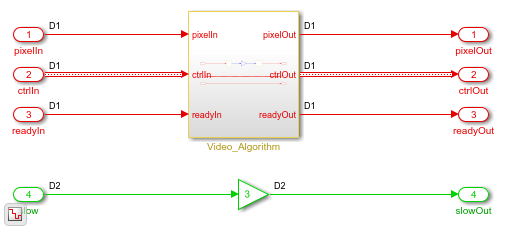

In this model, the DUT ports corresponding to inputs and outputs of the Video_Algorithm run at the fastest rate.

open_system('hdlcoder_axi_video_multirate/Multirate_DUT')

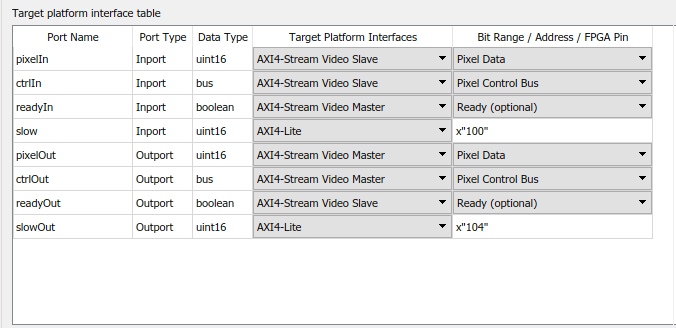

These ports can therefore map to AXI4-Stream Video interfaces. Part of the design running outside this algorithm corresponding to input slow and output slowOut running at a slower rate can map to AXI4 or AXI4-Lite interfaces. This figure shows an example of the target platform interface mapping for this model.

Note: To use the Pixel Control Bus Creator and Pixel Control Bus Selector blocks, you must have Vision HDL Toolbox™ installed. If you do not have Vision HDL Toolbox, use Bus Creator and Bus Selector blocks instead.

See also Model Design for AXI4-Stream Video Interface Generation.

Apply Optimizations to Part of Design Running at Slow Rate

With multirate support, you can apply optimizations such as resource sharing to a part of the design running at a slower rate. Make sure that the optimizations do not introduce a faster rate in your Simulink™ model. This example illustrates mapping to AXI4-Stream interfaces but you can map to AXI4-Stream Video or AXI4 Master interfaces by using this approach.

For an example, open the model hdlcoder_axi_multirate_sharing

load_system('hdlcoder_axi_multirate_sharing') set_param('hdlcoder_axi_multirate_sharing','SimulationCommand','update') open_system('hdlcoder_axi_multirate_sharing/DUT')

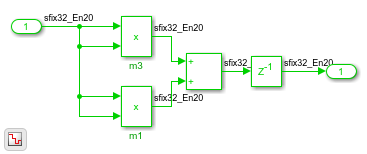

In this model, the Subsystem contains a simple multiply-add algorithm running at a slower rate.

open_system('hdlcoder_axi_multirate_sharing/DUT/Subsystem')

Resource sharing can be applied to this part of the design. To see the parameters saved on this Subsystem, run hdlsaveparams.

hdlsaveparams('hdlcoder_axi_multirate_sharing/DUT/Subsystem')

%% Set Model 'hdlcoder_axi_multirate_sharing' HDL parameters

hdlset_param('hdlcoder_axi_multirate_sharing', 'HDLSubsystem', 'hdlcoder_axi_multirate_sharing/DUT');

hdlset_param('hdlcoder_axi_multirate_sharing', 'ReferenceDesign', 'Default system with AXI4-Stream interface');

hdlset_param('hdlcoder_axi_multirate_sharing', 'ResetType', 'Synchronous');

hdlset_param('hdlcoder_axi_multirate_sharing', 'SynthesisTool', 'Xilinx Vivado');

hdlset_param('hdlcoder_axi_multirate_sharing', 'SynthesisToolChipFamily', 'Zynq');

hdlset_param('hdlcoder_axi_multirate_sharing', 'SynthesisToolDeviceName', 'xc7z020');

hdlset_param('hdlcoder_axi_multirate_sharing', 'SynthesisToolPackageName', 'clg484');

hdlset_param('hdlcoder_axi_multirate_sharing', 'SynthesisToolSpeedValue', '-1');

hdlset_param('hdlcoder_axi_multirate_sharing', 'TargetDirectory', 'hdl_prj\hdlsrc');

hdlset_param('hdlcoder_axi_multirate_sharing', 'TargetFrequency', 50);

hdlset_param('hdlcoder_axi_multirate_sharing', 'TargetPlatform', 'ZedBoard');

hdlset_param('hdlcoder_axi_multirate_sharing', 'Workflow', 'IP Core Generation');

% Set SubSystem HDL parameters

hdlset_param('hdlcoder_axi_multirate_sharing/DUT/Subsystem', 'SharingFactor', 3);

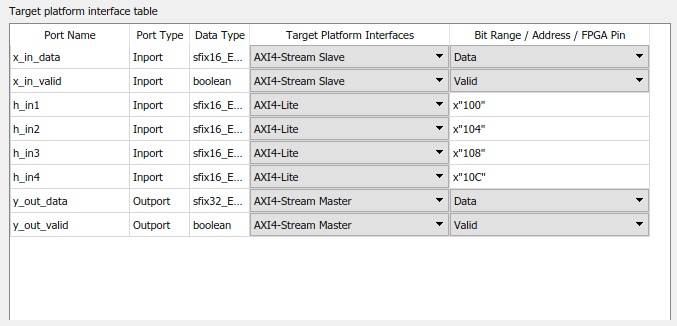

You can map the DUT interface ports to AXI4-Stream Master or AXI4-Stream Slave interfaces. This figure shows an example of the target platform interface mapping for this model.