Generate Multirate HDL Code to Decimate Input Signal Using DSP System Toolbox Blocks

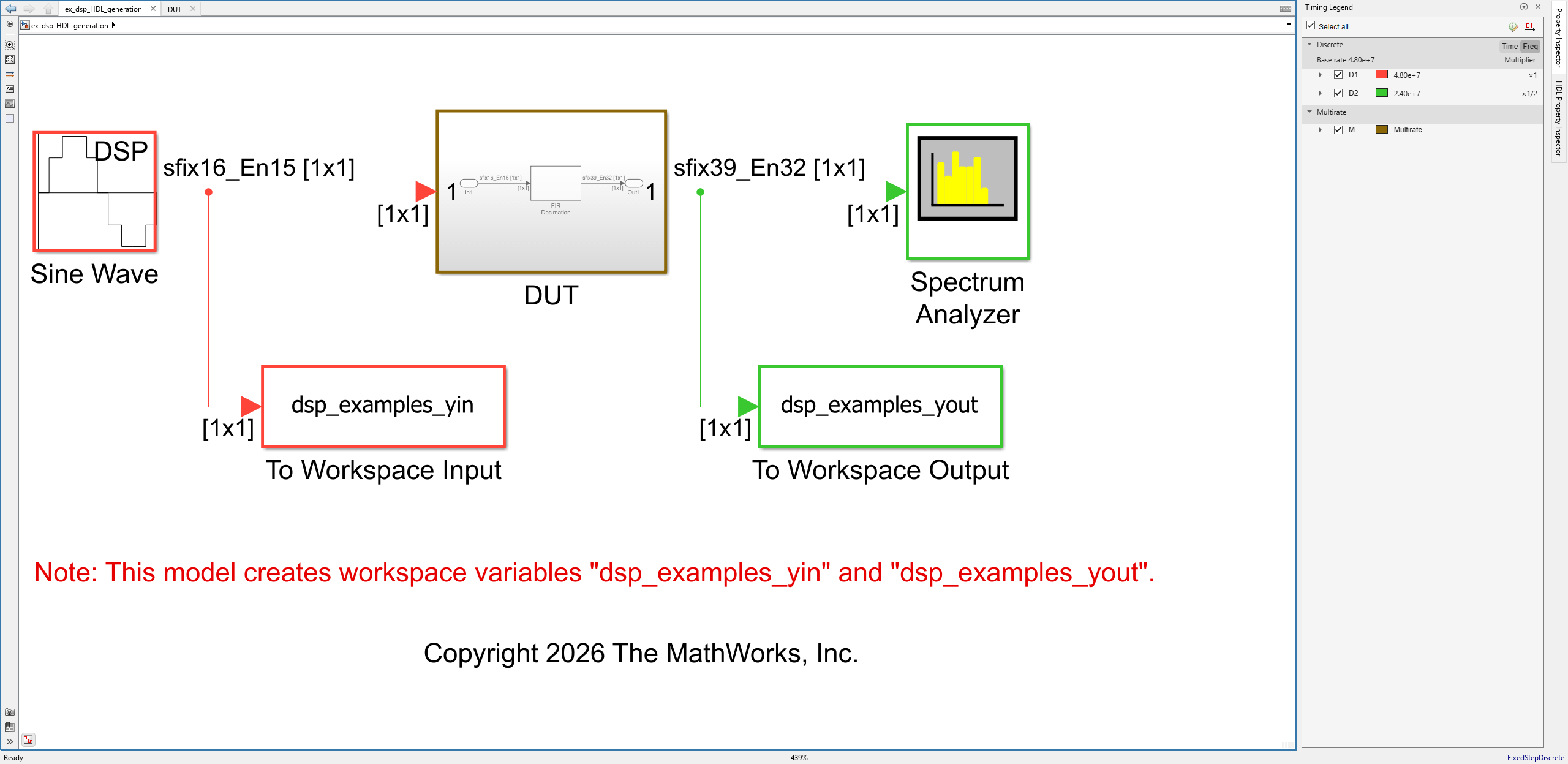

This example shows how to generate HDL code from a model using DSP System Toolbox® blocks. When you generate HDL code from a model using DSP System Toolbox blocks, HDL Coder™ maps Simulink® sample time settings to clock enable signals in generated HDL code.

The model in this example decimates an 8e5 Hz sinusoid signal sampled at a sampling frequency of 48e6 Hz by a factor of 2 using the DSP System Toolbox block FIR Decimation.

load_system('ex_dsp_HDL_generation') open_system('ex_dsp_HDL_generation/DUT')

In this design, the sample rate of the signal after decimation is 24e6 Hz, half the sample rate of the signal before the operation.

When you run makehdl on the DUT, HDL Coder® creates a generated model for code generation, gm_ex_dsp_HDL_generation.slx, and generates HDL code:

makehdl('ex_dsp_HDL_generation/DUT')### Working on the model ex_dsp_HDL_generation ### Generating HDL for ex_dsp_HDL_generation/DUT ### Using the config set for model ex_dsp_HDL_generation for HDL code generation parameters. ### Running HDL checks on the model 'ex_dsp_HDL_generation'. ### Begin compilation of the model 'ex_dsp_HDL_generation'... ### Working on the model 'ex_dsp_HDL_generation'... ### Working on... GenerateModel ### Begin model generation 'gm_ex_dsp_HDL_generation'... ### Copying DUT to the generated model.... ### Model generation complete. ### Generated model saved at hdlsrc/ex_dsp_HDL_generation/gm_ex_dsp_HDL_generation.slx ### Begin VHDL Code Generation for 'ex_dsp_HDL_generation'. ### Begin VHDL Code Generation for 'DUT_tc'. ### Working on DUT_tc as hdlsrc/ex_dsp_HDL_generation/DUT_tc.vhd. ### Code Generation for 'DUT_tc' completed. ### Working on ex_dsp_HDL_generation/DUT/FIR Decimation as hdlsrc/ex_dsp_HDL_generation/FIR_Decimation.vhd. ### Working on ex_dsp_HDL_generation/DUT as hdlsrc/ex_dsp_HDL_generation/DUT.vhd. ### Generating package file hdlsrc/ex_dsp_HDL_generation/DUT_pkg.vhd. ### Code Generation for 'ex_dsp_HDL_generation' completed. ### Generating HTML files for code generation report at index.html ### Creating HDL Code Generation Check Report DUT_report.html ### HDL check for 'ex_dsp_HDL_generation' complete with 0 errors, 0 warnings, and 0 messages. ### HDL code generation complete.

In this design, HDL Coder generates two clock enable signals corresponding to the two sample times in the DUT. One for the model base rate, enb, and one for the two-fold slower decimation logic, enb_1_2_1. View the generated enable signals in the timing controller, DUT_tc.vhd.

file = fullfile("hdlsrc","ex_dsp_HDL_generation","DUT_tc.vhd"); coder.example.extractLines(file,"-- Master","phase 1",1,1)

-- Master clock enable input: clk_enable -- -- enb : identical to clk_enable -- enb_1_2_1 : 2x slower than clk with phase 1

For more information on how the timing controller works, see Timing Controller for Multirate Models.

To learn more about using HDL Coder to generate code from models that use DSP System Toolbox, see HDL Code Generation (DSP System Toolbox).

See Also

FIR Decimation (DSP System Toolbox)

Topics

- Code Generation from Multirate Models

- HDL Code Generation (DSP System Toolbox)

- Multichannel FIR Filter for FPGA (DSP System Toolbox)