CORDIC Sigmoid HDL Optimized

Compute CORDIC-based sigmoid activation and generate optimized HDL code

Since R2024a

Libraries:

Fixed-Point Designer HDL Support /

Math Operations

Description

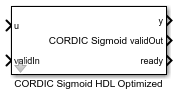

The CORDIC Sigmoid HDL Optimized block returns the sigmoid activation of u, computed using a CORDIC-based implementation optimized for HDL code generation.

Examples

This example demonstrates how to compute the sigmoid activation of a given real-valued set of data using the CORDIC Sigmoid HDL Optimized block.

Algorithm

The sigmoid function is defined by

which is equivalent to

The core algorithm of this block uses the CORDIC algorithm in hyperbolic rotation mode to compute the Hyperbolic Tangent HDL Optimized (tanh).

Supported Data Types

The CORDIC Sigmoid HDL Optimized block supports single, double, binary-point scaled fixed-point, and binary-point scaled-double data types for simulation. However, only binary-point scaled fixed-point data types are supported for HDL code generation.

I/O Interface

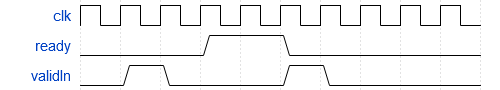

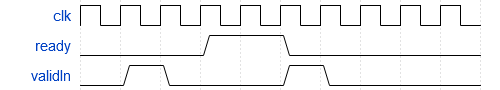

The CORDIC Sigmoid HDL Optimized block accepts data when the ready output is high, indicating that the block is ready to begin a new computation. Use validIn to indicate a valid input. If the block successfully registers the input value it will de-assert the ready signal; you must then wait until the signal is asserted again to send a new input. This protocol is summarized in the following wave diagram. Note how the first valid input to the block is discarded because the block was not ready to accept input data.

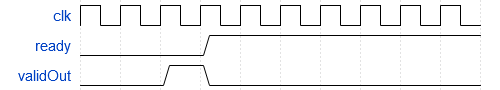

When the block has finished the computation and is ready to send the output, it will assert validOut for one clock cycle. Then ready will be asserted, indicating that the block is ready to accept a new input value.

Simulate the Model

Open the CORDICSigmoidModel model.

mdl = 'CORDICSigmoidModel';

open_system(mdl)

The model contains the CORDIC Sigmoid HDL Optimized block connected to a data source which takes in an array of inputs and passes an input value from the array to the CORDIC Sigmoid HDL Optimized block when it is ready to accept a new input. The output computed for each value is stored in a workspace variable. The simulation terminates when all inputs have been processed.

Define an array of inputs.

x = fi(linspace(-10,10,100));

Simulate the model.

sim(mdl);

When the simulation is complete, a new workspace variable, sigmoidOutput, is created to hold the computed value for each input.

Plot the Output

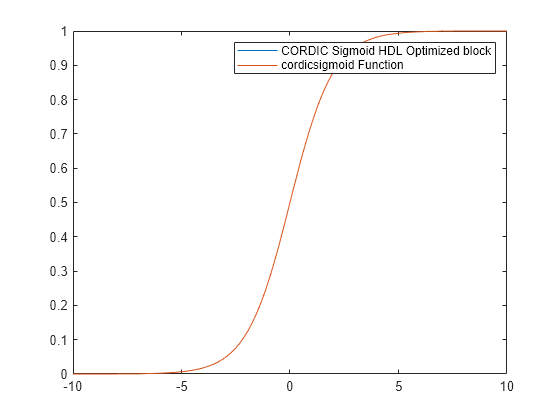

Plot the error of the calculation by comparing the output of the CORDIC Sigmoid HDL Optimized block to that of the MATLAB® cordicsigmoid function.

yMATLAB = cordicsigmoid(x); yMATLAB.numerictype

ans =

DataTypeMode: Fixed-point: binary point scaling

Signedness: Signed

WordLength: 16

FractionLength: 14

sigmoidOutput.numerictype

ans =

DataTypeMode: Fixed-point: binary point scaling

Signedness: Signed

WordLength: 16

FractionLength: 14

figure(1); plot(x, sigmoidOutput); hold on plot(x, yMATLAB); legend('CORDIC Sigmoid HDL Optimized block','cordicsigmoid Function');

Verify the block output is bit-exact with the output of the cordicsigmoid function.

max(yMATLAB' - sigmoidOutput)

ans =

0

DataTypeMode: Fixed-point: binary point scaling

Signedness: Signed

WordLength: 17

FractionLength: 14

Ports

Input

Input data, specified as a real-valued scalar.

If u is a fixed-point or scaled double data type, u must use binary-point scaling. Slope-bias representation is not supported for fixed-point data types. Only binary-point scaled fixed-point data types are supported for code generation.

Data Types: single | double | fixed point

Whether input is valid, specified as a Boolean scalar. This control signal

indicates when the data from the u input port is valid. When this value

is 1 (true), the block captures the value on the

u input port. When this value is 0

(false), the block ignores the input samples.

Data Types: Boolean

Output

Sigmoid activation of the value at u, returned as a scalar. The value at y is the CORDIC-based approximation of the sigmoid activation of u.

When the input u is floating point, the output y has the same data type as the input. When the input is a fixed-point data type, the output has the same word length as the input and a fraction length equal to 2 less than the word length.

Data Types: single | double | fixed point

Whether the output data is valid, returned as a Boolean scalar. When the value of

this control signal is 1 (true), the block has

successfully computed the output y. When this value is

0 (false), the output data is not

valid.

Data Types: Boolean

Whether the block is ready, returned as a Boolean scalar. This control signal

indicates when the block is ready for new input data. When this value is 1

(true), and the validIn value is 1

(true), the block accepts input data in the next clock cycle.

When this value is 0 (false), the block ignores input data in the

next clock cycle.

Data Types: Boolean

Algorithms

CORDIC is an acronym for COordinate Rotation DIgital Computer. The Givens rotation-based CORDIC algorithm is one of the most hardware-efficient algorithms available because it requires only iterative shift-add operations (see References). The CORDIC algorithm eliminates the need for explicit multipliers.

The precision of the CORDIC algorithm is a function of the data type used and the maximum shift value or number of iterations of the CORDIC kernel. Using a data type with a larger word length and performing more iterations of the CORDIC algorithm can reduce the numeric error of the result. However, doing so also increases the latency of the computation and the utilizes more hardware resources. For more information, see How to Set CORDIC Input Word Length and Maximum Shift Value to Achieve Desired Precision.

This block automatically determines the number of iterations, niters,

the CORDIC algorithm performs based on the data type of the input.

| Data type of input x | niters |

|---|---|

| single | 23 |

| double | 52 |

| fixed point | One less than the word length of u. The minimum number

of CORDIC iterations is 7. |

The CORDIC Sigmoid HDL Optimized block accepts data when the ready output is high, indicating that the block is ready to begin a new computation. To send input data to the block, the validIn signal must be asserted. If the block successfully registers the input value it will de-assert the ready signal, and you must then wait until the signal is asserted again to send a new input. This protocol is summarized in the following wave diagram. Note how the first valid input to the block is discarded because the block was not ready to accept input data.

When the block has finished the computation and is ready to send the output, it will assert validOut for one clock cycle. Then ready will be asserted, indicating that the block is ready to accept a new input value.

This block supports HDL code generation using the Simulink® HDL Workflow Advisor. For an example, see HDL Code Generation and FPGA Synthesis from Simulink Model (HDL Coder) and Implement Digital Downconverter for FPGA (DSP HDL Toolbox).

This example data was generated by synthesizing the block on a Xilinx® Zynq®-7000 xc7z045 SoC. The synthesis tool was Vivado® v2023.1 (win64).

The following parameters were used for synthesis.

Input data type:

sfix16_en10Target frequency: 200 MHz

| Resource | Usage | Available | Utilization (%) |

|---|---|---|---|

| Slice LUTs | 2516 | 218600 | 1.15 |

| Slice Registers | 733 | 437200 | 0.17 |

| DSPs | 0 | 900 | 0.00 |

| Block RAM Tile | 0 | 545 | 0.00 |

| URAM | 0 | 0 |

Value | |

|---|---|

| Requirement | 5 ns (200 MHz) |

| Data Path Delay | 4.815 ns |

| Slack | 0.166 ns |

| Clock Frequency | 206.87 MHz |

References

[1] Volder, Jack E. “The CORDIC Trigonometric Computing Technique.” IRE Transactions on Electronic Computers EC-8, no. 3 (Sept. 1959): 330–334.

[2] Andraka, Ray. “A Survey of CORDIC Algorithm for FPGA Based Computers.” In Proceedings of the 1998 ACM/SIGDA Sixth International Symposium on Field Programmable Gate Arrays, 191–200. https://dl.acm.org/doi/10.1145/275107.275139.

[3] Walther, J.S. “A Unified Algorithm for Elementary Functions.” In Proceedings of the May 18-20, 1971 Spring Joint Computer Conference, 379–386. https://dl.acm.org/doi/10.1145/1478786.1478840.

[4] Schelin, Charles W. “Calculator Function Approximation.” The American Mathematical Monthly, no. 5 (May 1983): 317–325. https://doi.org/10.2307/2975781.

Extended Capabilities

Slope-bias representation is not supported for fixed-point data types.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| General | |

|---|---|

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

Only binary-point scaled fixed-point data types are supported for code generation.

Version History

Introduced in R2024a

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)