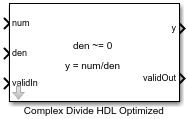

Complex Divide HDL Optimized

Divide one input by another using CORDIC algorithm and generate optimized HDL code

Libraries:

Fixed-Point Designer HDL Support /

Math Operations

Description

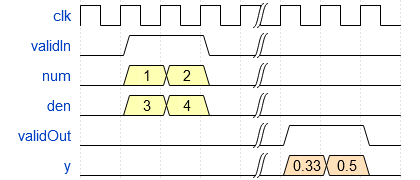

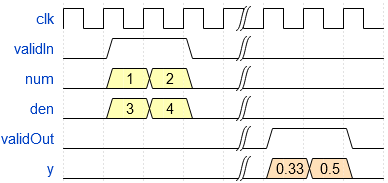

The Complex Divide HDL Optimized block outputs the result of dividing the scalar num by the scalar den, such that y = num/den.

Examples

Limitations

Data type override is not supported for the Complex Divide HDL Optimized block.

Ports

Input

Output

Parameters

Tips

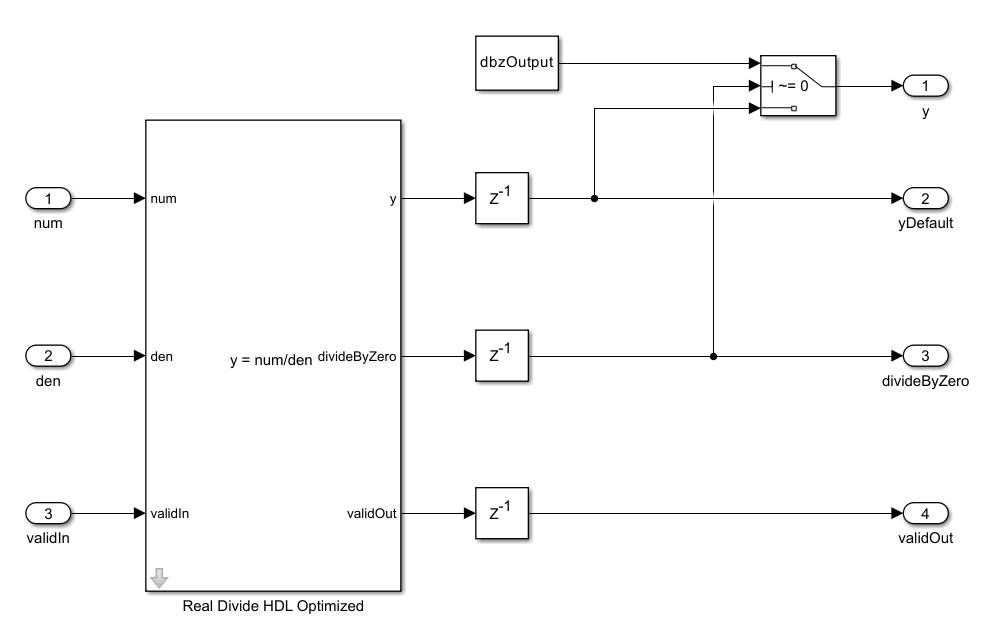

The blocks Divide by Constant HDL Optimized, Real Divide HDL Optimized, and Complex Divide HDL Optimized all perform the division operation and generate optimized HDL code.

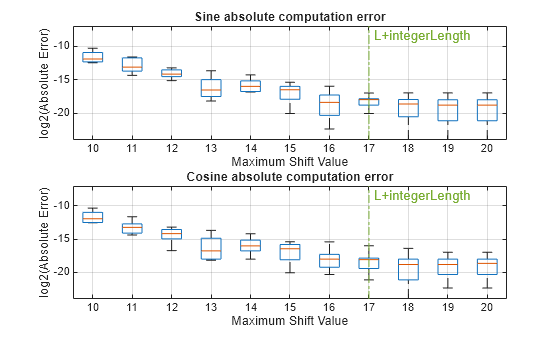

Real Divide HDL Optimized and Complex Divide HDL Optimized are based on a CORIDC algorithm. These blocks accept a wide variety of inputs, but will result in greater latency.

Divide by Constant HDL Optimized accepts only real inputs and a constant divisor. Use of this block consumes DSP slices, but will complete the division operation in fewer cycles and at a higher clock rate.

The behaviors of the Real Divide HDL Optimized and Complex Divide HDL Optimized blocks are equivalent to

when the inputs[y,dbz] = embblk.divide.cordicDivide(num,den,OutputType,maximumShiftValue)

numanddenare real or complex values, respectively. If the input data type is fixed point with binary-point scaling, the function and blocks produce bit-exact results. If the input data type is floating point, the function and the block can have small numerical differences.

Algorithms

References

[1] Volder, Jack E. “The CORDIC Trigonometric Computing Technique.” IRE Transactions on Electronic Computers EC-8, no. 3 (Sept. 1959): 330–334.

[2] Andraka, Ray. “A Survey of CORDIC Algorithm for FPGA Based Computers.” In Proceedings of the 1998 ACM/SIGDA Sixth International Symposium on Field Programmable Gate Arrays, 191–200. https://dl.acm.org/doi/10.1145/275107.275139.

[3] Walther, J.S. “A Unified Algorithm for Elementary Functions.” In Proceedings of the May 18-20, 1971 Spring Joint Computer Conference, 379–386. https://dl.acm.org/doi/10.1145/1478786.1478840.

[4] Schelin, Charles W. “Calculator Function Approximation.” The American Mathematical Monthly, no. 5 (May 1983): 317–325. https://doi.org/10.2307/2975781.