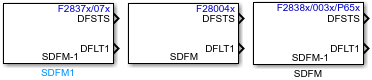

F2807x/F2837xD/F2837xS/F28004x/F28003x/F2838x/F28p65x SDFM

Configure filter channel for SDFM Module

Libraries:

C2000 Microcontroller Blockset /

F28003x

C2000 Microcontroller Blockset /

F28004x

C2000 Microcontroller Blockset /

F2807x

C2000 Microcontroller Blockset /

F2837xD

C2000 Microcontroller Blockset /

F2837xS

C2000 Microcontroller Blockset /

F2838x /

C28x

C2000 Microcontroller Blockset /

F28p65x

Description

The sigma delta filter module (SDFM) is a four-channel digital filter designed specifically for current measurement and resolver position decoding in motor control applications. Each input channel can receive an independent delta-sigma (ΔΣ) modulator bit stream. The bit streams are processed by four individually-programmable digital decimation filters.

The filter set includes a fast comparator (secondary filter) for immediate digital threshold comparisons for over-current and under-current monitoring and a primary data filter.

Each SDFM module consists of:

Four independent configurable primary filter (data filter) units.

Four independent, configurable secondary filter (comparator) units.

Eight external pins (four sigma-delta data input pins and four sigma-delta clock input pins).

Four different configurable modulator clock modes.

For more information on configuring filter channels, refer to SDFM Configuration Parameters.

Ports

Output

Parameters

Version History

Introduced in R2020b