Buck Power Train Design Workflow

This example shows how to use the MathWorks® switched mode power supply (SMPS) workflow to design a power supply with a buck power train.

The buck power train circuit topology is one of the most basic SMPS power train topologies, used to convert an input DC voltage to a lower DC output voltage with the same polarity. You can use the MathWorks SMPS workflow to design the buck power train for a specified operating point or range of operating points, design a proportional-integral-derivative (PID) compensator to control the output voltage, and simulate the power supply's behavior in dynamic conditions.

This example uses the buck power train circuit shown in the schematic diagram below and defined in BuckPowerTrain.slx.

powerTrain = "BuckPowerTrain";

open_system(powerTrain);

Operating Point Analysis

You can use operating point analysis to design the power train and analyze its performance under steady state operating conditions. For a detailed walkthrough of this process, see Boost Power Train Operating Point Analysis.

cfg = cktconfig(powerTrain, ... CircuitDesignName=powerTrain, ... Ports=["cQ1","Vg","Iload","Vin","Vout","Iout","Ig"]); [results,~,waves] = cktoperpoint(cfg, ... OutputPort='Vout', ... % Must be a character vector OutputValues=[10 12], ... DutyCycle=[0.1 0.9], ... Frequency=100000, ... ControlVariable="Duty cycle", ... InputValues={ ... "Iload","Vg"; ... 0, 28});

Run the function getPowerTrainMetrics included with this example to get power and efficiency metrics for the power train.

results = getPowerTrainMetrics(cfg,waves,results,"Vin","Ig","Vout","Iout");

DC Results Table

results(:,1:7)

ans =

2×7 table

Duty Cycle Frequency Vg Iload Vin Vout Iout

__________ _________ __ _____ ______ ____ ____

0.28881 1e+05 28 0 27.998 10 0.4

0.36555 1e+05 28 0 27.998 12 0.48

Power Analysis Table

results(:,8:13)

ans =

2×6 table

Ig P_Vg P_Iload P_Rg P_Rload P_total

_______ _______ _______ _________ _______ ________

0.15036 -4.2438 0 0.0010517 4 -0.24271

0.21397 -6.0464 0 0.0016873 5.7601 -0.28469

Efficiency and Ripple Metrics

results(:,14:end)

ans =

2×5 table

Efficiency Vin_ripple Iin_ripple Vout_ripple Iout_ripple

__________ __________ __________ ___________ ___________

0.94279 0.0104 1.04 0.011098 0.0004439

0.9529 0.01171 1.171 0.012466 0.00049862

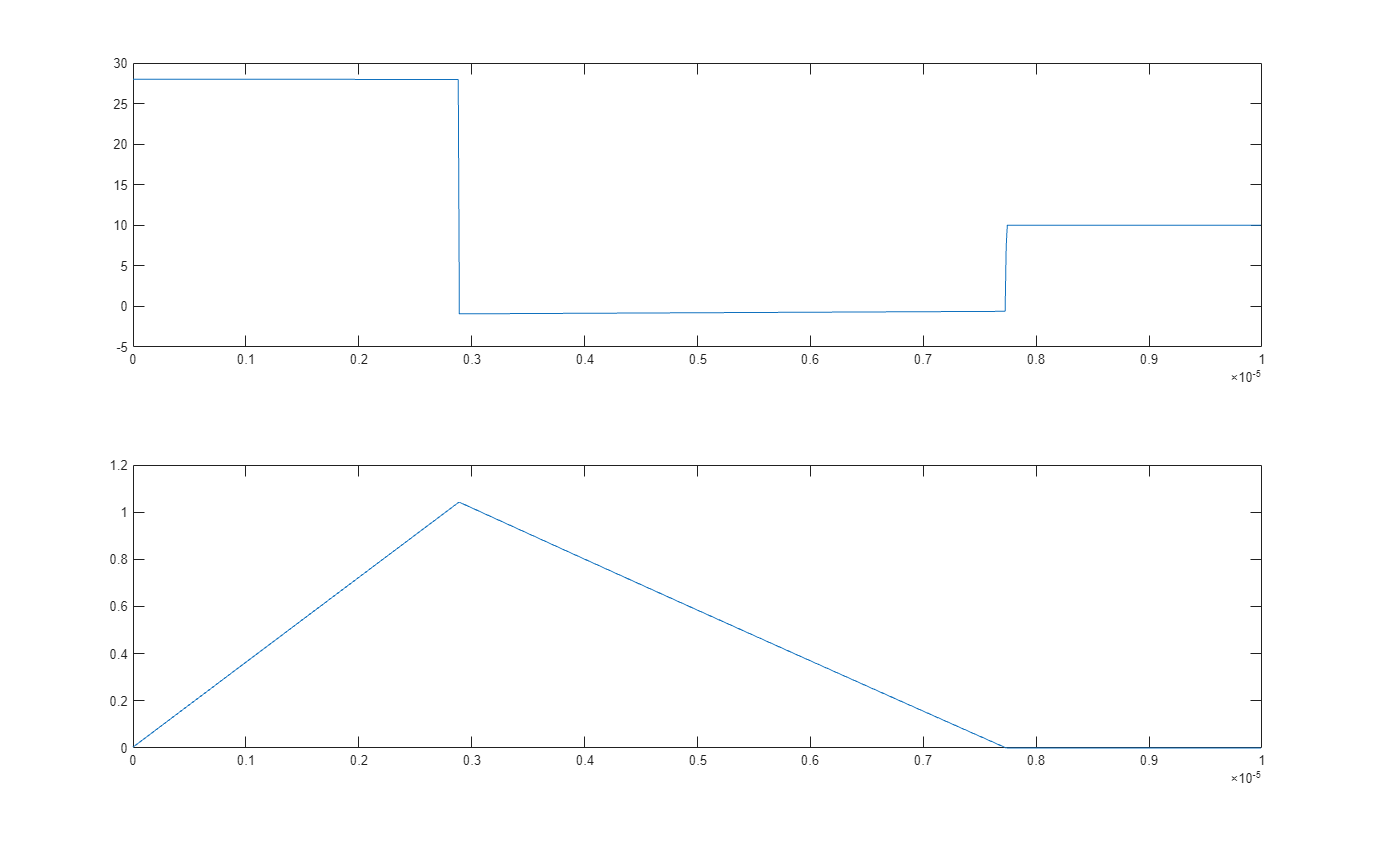

The waves table provides access to all of the steady state voltage and current waveforms in the power train circuit, and you can use these waveforms to gain insights into the way the circuit operates. For example, the waveform at the switching node (V4) of the circuit demonstrates the effect of the switching device and diode on the input voltage of the inductor. When the switching device is turned on, it draws current from the input supply, through the inductor and into the decoupling capacitor and load. During this period, the switching node is at a higher voltage than the output, causing the current in the inductor to increase. However when the switching device is turned off, the only current path available to the inductor is the diode to the return node. Since the current must continue to flow, the inductor drives the diode's negative terminal below the return voltage. This causes the inductor current to decrease, but it continues to flow unless and until the current in the diode reaches zero, turning the diode off.

Switching Node Waveforms

t = waves{1}.Time;

vswitch = waves{1}.("V4");

iL1 = waves{1}.iL1;

figure(1);

tiledlayout(2,1);

% Inductor output voltage

nexttile;

plot(t,vswitch);

title(powerTrain + " Switching Node Waveform");

% Inductor current

nexttile;

plot(t,iL1);

title(powerTrain + " Inductor Current");

Compensator Design

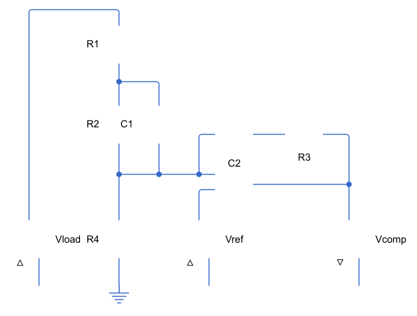

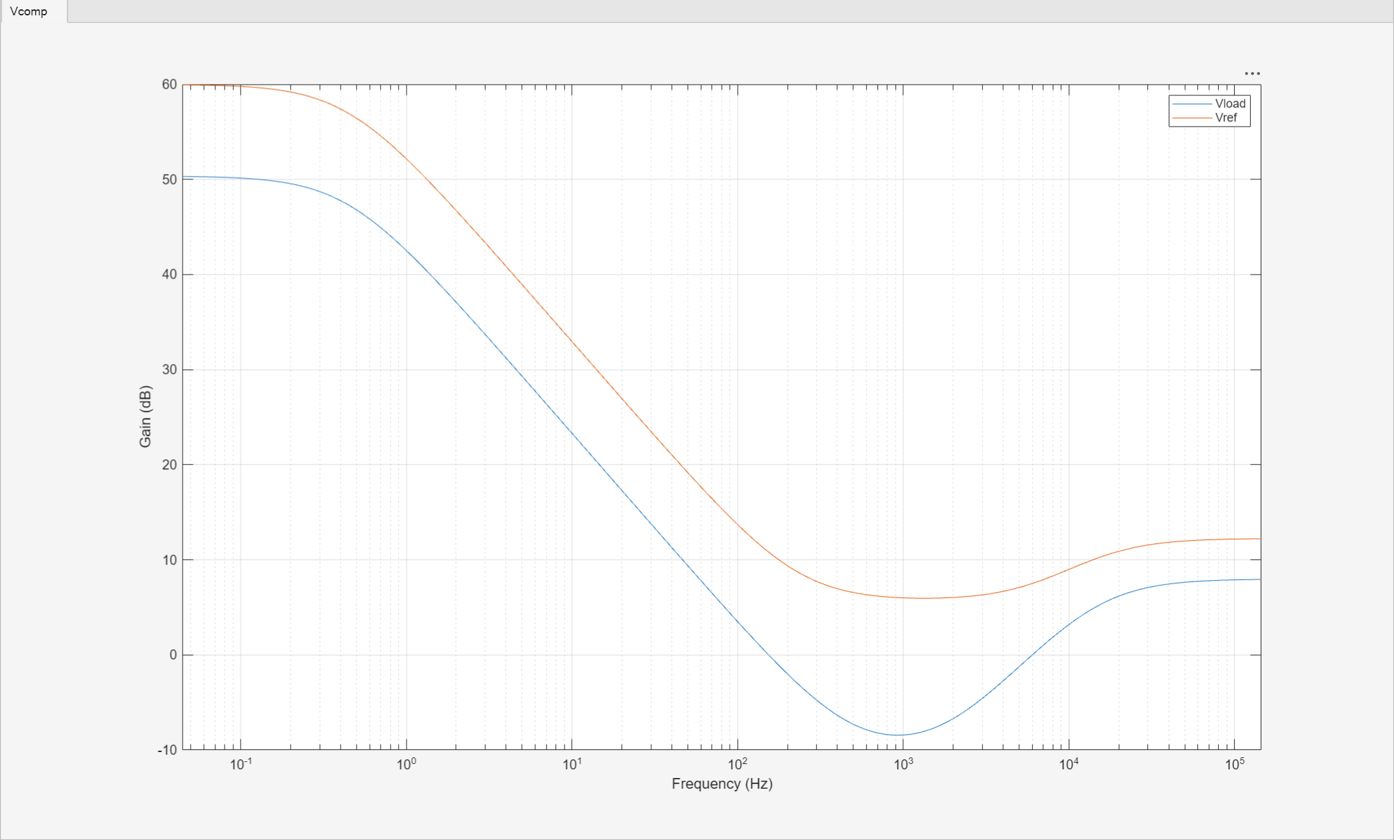

Reference [1] explains how to design a PID controller to control a buck power train. The PID compensator circuit shown in the schematic below and defined in PIDCompensator.slx was designed using the method given in [1].

compensator = "PIDCompensator";

open_system(compensator);

You can obtain the poles, zeros and symbolic model of this circuit and optimize its design by applying the method described in the Feedback Amplifier Design for Voltage-Mode Boost Converter example.

cktzpk(compensator,"DisplayPlot",true);

Time Domain Simulation

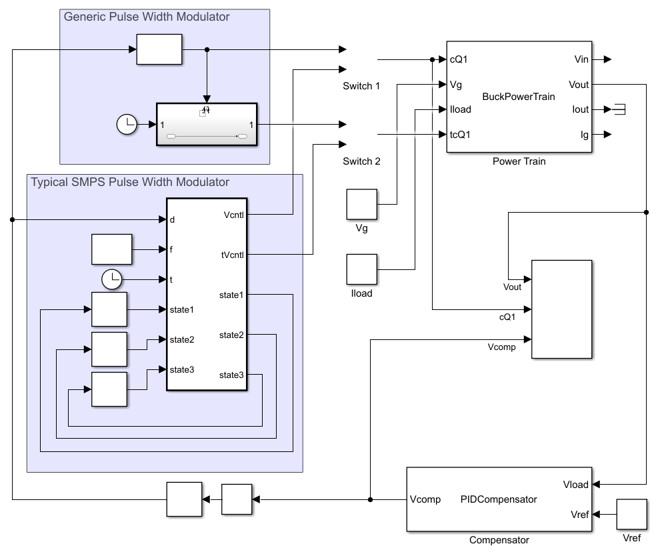

You can combine the power train Simulink block from the operating point analysis with the compensator Simulink block from the controller design and a pulse width modulator (PWM) to be discussed in this section to create a time domain simulation of the closed loop behavior of the power supply.

Open the model BuckPowerSupply.slx, which contains the setup to test the buck power train and its controller simultaneously.

close all powerSupplyModel = "BuckPowerSupply"; open_system(powerSupplyModel);

You can use cktblock to build a Simulink® block to implement a time domain behavioral model of the power train circuit. Do so, and connect the resulting block to its inputs and outputs in the power supply model. Set BlockName to Power Train to replace the existing Power Train block.

cktblock(cfg,powerSupplyModel, ... BlockName="Power Train"); set_param(powerSupplyModel + "/Power Train", ... Position=[395 2 540 113], ... InheritSampleRate="off", ... SampleRate="2.5e6");

Do the same for the compensator circuit: create the block using cktblock and connect it to the provided inputs and outputs.

cktblock(compensator,powerSupplyModel, ... CircuitDesignName=compensator, ... BlockName="Compensator", ... Ports=["Vload","Vref","Vcomp"]); set_param(powerSupplyModel + "/Compensator", ... Position=[355 428 540 492], ... Orientation="left");

The PWM interacts with ripple at the output of the compensator, making details of the PWM definition important. While most analyses ignore any ripple that passes from the output of the power train to the output of the compensator, there can be ripple at the output of the compensator that significantly affects the closed loop behavior of the power supply. Power train output ripple is inherently synchronous with the control signal provided by the PWM, and so any delay between the time the PWM derives the width of the next pulse from the compensator output and the time the PWM outputs that pulse will increase the delay in the control loop and reduce the phase margin. Ripple at the compensator output also appears to affect the small signal behavior of the control loop in other ways that should be evaluated through analysis of time domain simulation results.

The model BuckPowerSupply enables you to switch between two different PWMs.

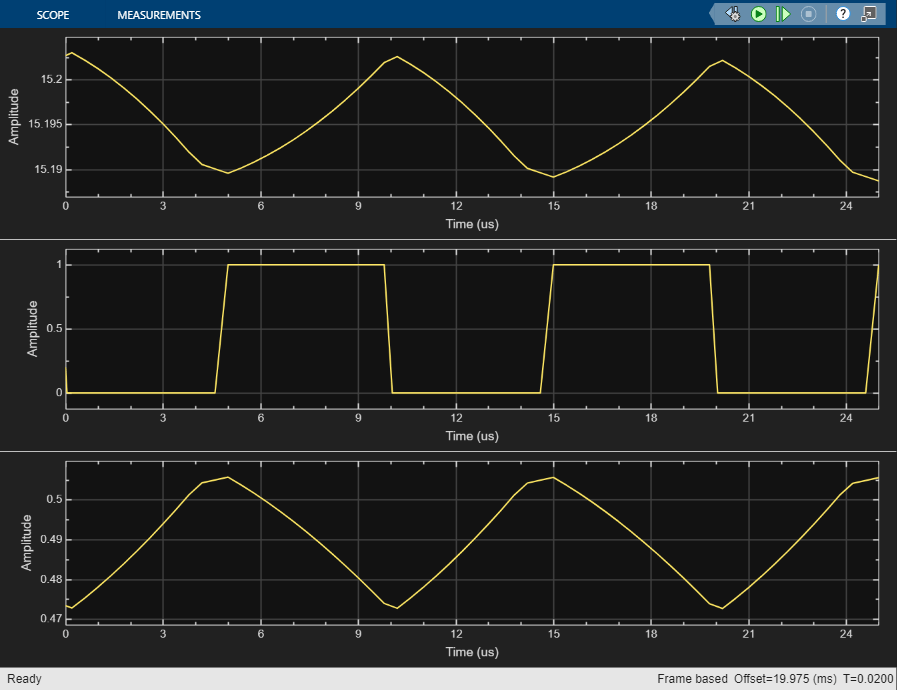

The first choice offered is the Simulink PWM block, which reads the output pulse width from the control input on the rising edge of the output pulse. To use this PWM, set the manual switches Switch 1 and Switch 2 in the model to their upper positions. Run this model and compare the steady state outputs of the power train output and the compensator to the output of the PWM. Note that the steady state duty cycle occurs near the beginning of the ripple cycle and that the ripple voltage increases from there.

set_param(powerSupplyModel + "/Switch 1",sw="1"); set_param(powerSupplyModel + "/Switch 2",sw="1"); sim(powerSupplyModel);

Many texts on SMPS specify the PWM circuit shown below explicitly and in detail for voltage controlled operation. Note that in this circuit the falling edge of the PWM output occurs essentially as soon as the sawtooth ramp has become higher than the compensator output.

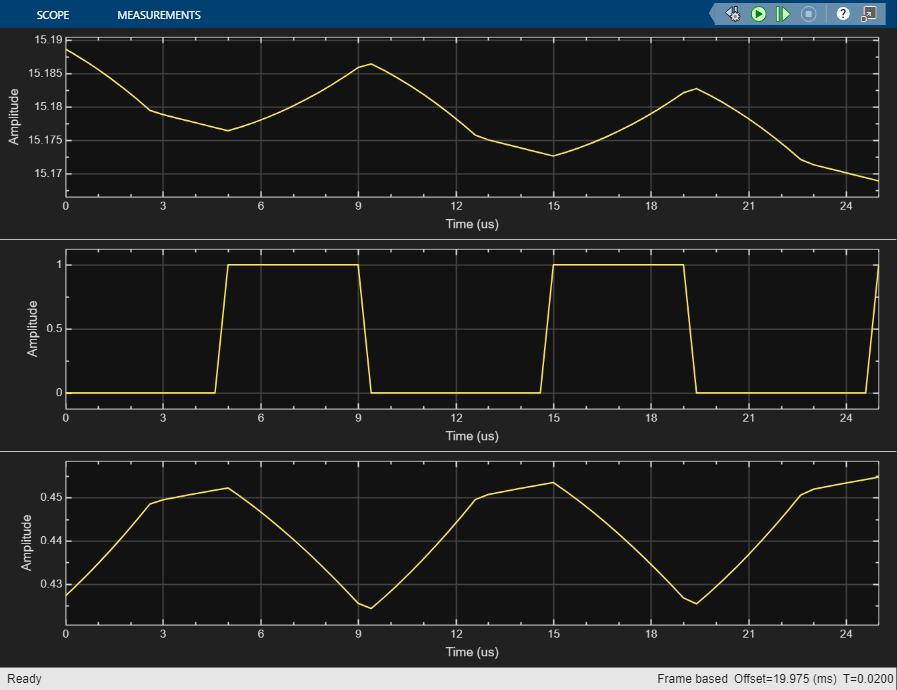

The other PWM choice in the model BuckPowerSupply uses a MATLAB® function block and several unit delay blocks to closely approximate the behavior of this circuit. To use this PWM, set the manual switches Switch 1 and Switch 2 in the model to their lower positions. Run BuckPowerSupply and note that the falling edge of the PWM output occurs at the peak of the compensator output ripple waveform, and that the value at that point is equal to the steady state output duty cycle.

set_param(powerSupplyModel + "/Switch 1",sw="0"); set_param(powerSupplyModel + "/Switch 2",sw="0"); sim(powerSupplyModel);

References

1. R. W. Erickson and D. Maksimovic, Fundementals of Power Electronics, 3rd, Ed., Cham, Switzerland: Springer Nature, 2020.