Resource Sharing for Area Optimization

This example shows how to use the subsystem level sharing optimization in HDL Coder™.

Introduction

To implement area-efficient hardware, use resource sharing, which is a subsystem-level optimization supported by HDL Coder.

By default, HDL Coder implements hardware that is a one-to-one mapping of Simulink® blocks to hardware module implementations. The resource sharing optimization enables you to share hardware resources by enabling an N-to-1 mapping of N functionally equivalent Simulink blocks to a single hardware module. The user specifies N by using the SharingFactor implementation parameter.

Because a time-multiplexed architecture incurs a longer latency to complete the area optimization, HDL Coder manages the timing discrepancy depending on what resources are being shared. Suppose that the shared resources are operating at the base sample rate, and then resource sharing is implemented as a local multirate architecture, which is described in this example. If the shared resources are operating at a slower sample rate than the base sample rate, then HDL Coder invokes clock-rate pipelining to synthesize an implementation that uses the latency budget defined in the rate differential. In this case, the resource shared architecture is a single rate implementation and takes multiple time steps to complete all the shared operations. Single-Rate Resource Sharing Architecture describes the details of this implementation.

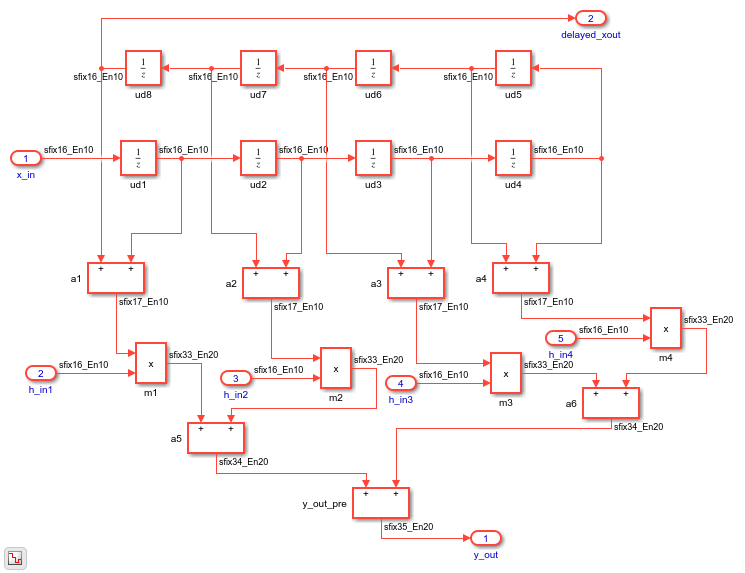

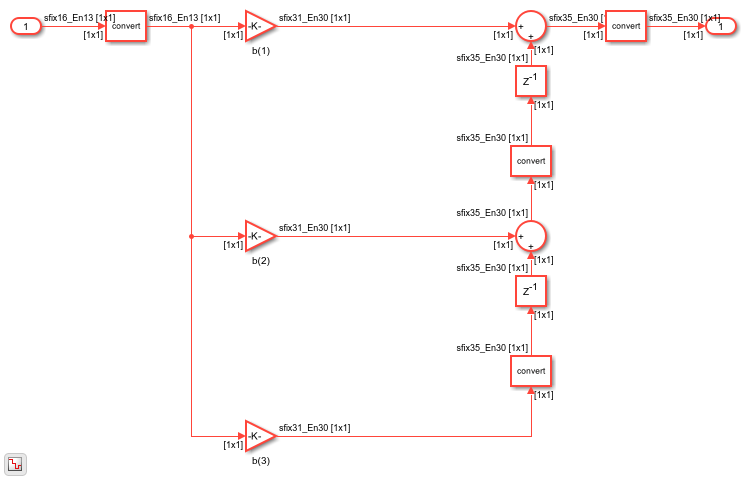

This example also illustrates the local multirate architecture of resource sharing. Consider the following symmetric FIR filter model. It contains four product blocks that are functionally equivalent and that map to four multipliers in hardware. The Resource Utilization Report lists the hardware resources used.

load_system('sfir_fixed'); open_system('sfir_fixed/symmetric_fir'); hdlset_param('sfir_fixed', 'ResourceReport', 'on'); makehdl('sfir_fixed/symmetric_fir');

### Working on the model <a href="matlab:open_system('sfir_fixed')">sfir_fixed</a>

### Generating HDL for <a href="matlab:open_system('sfir_fixed/symmetric_fir')">sfir_fixed/symmetric_fir</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('sfir_fixed', { 'HDL Code Generation' } )">sfir_fixed</a> for HDL code generation parameters.

### Running HDL checks on the model 'sfir_fixed'.

### Begin compilation of the model 'sfir_fixed'...

### Working on the model 'sfir_fixed'...

### Working on... <a href="matlab:configset.internal.open('sfir_fixed', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_sfir_fixed'...

### Copying DUT to the generated model....

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/sfir_fixed/gm_sfir_fixed.slx')">hdlsrc/sfir_fixed/gm_sfir_fixed.slx</a>

### Begin VHDL Code Generation for 'sfir_fixed'.

### Working on sfir_fixed/symmetric_fir as hdlsrc/sfir_fixed/symmetric_fir.vhd.

### Code Generation for 'sfir_fixed' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/sfir_fixed', '/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/sfir_fixed/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/sfir_fixed/symmetric_fir_report.html

### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.

Share Resources for an N-to-1 Mapping

To reduce area resources, you can invoke the sharing optimization by setting the SharingFactor parameter on the subsystem to a positive integer value. This parameter specifies N in the N-to-1 hardware mapping. In this example, there are four product blocks, so generating HDL with SharingFactor set to 4 generates HDL code that has one multiplier.

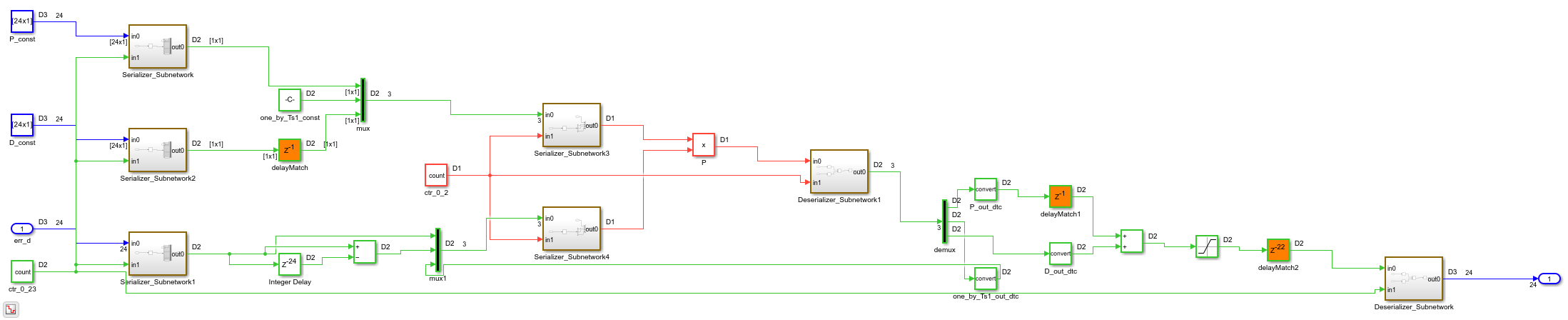

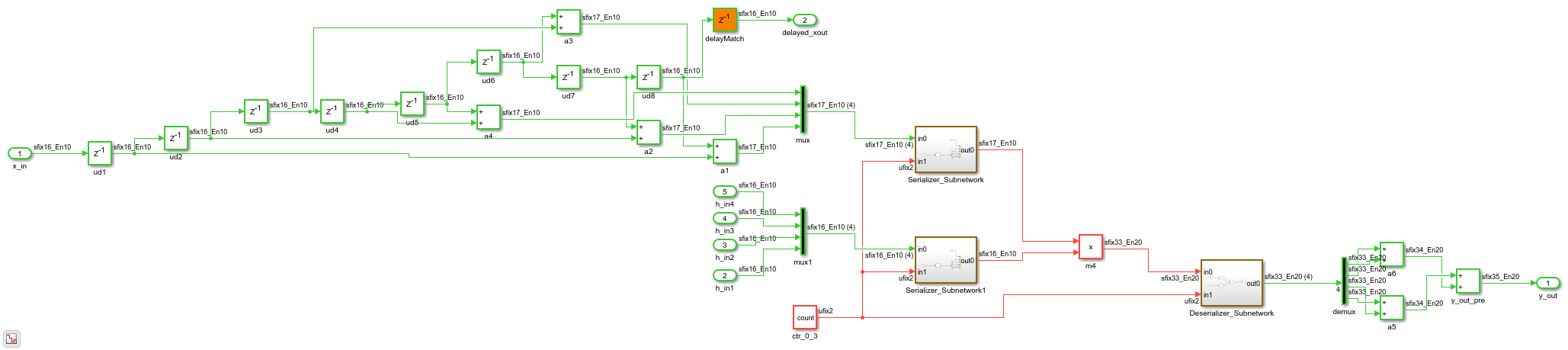

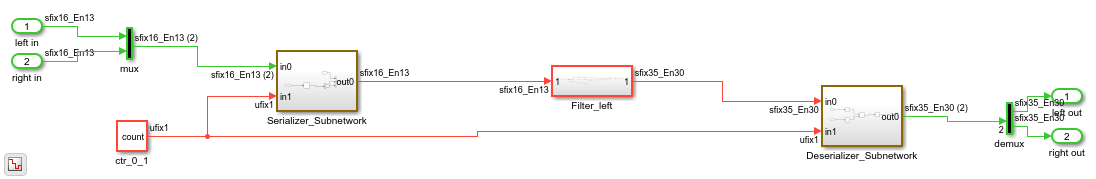

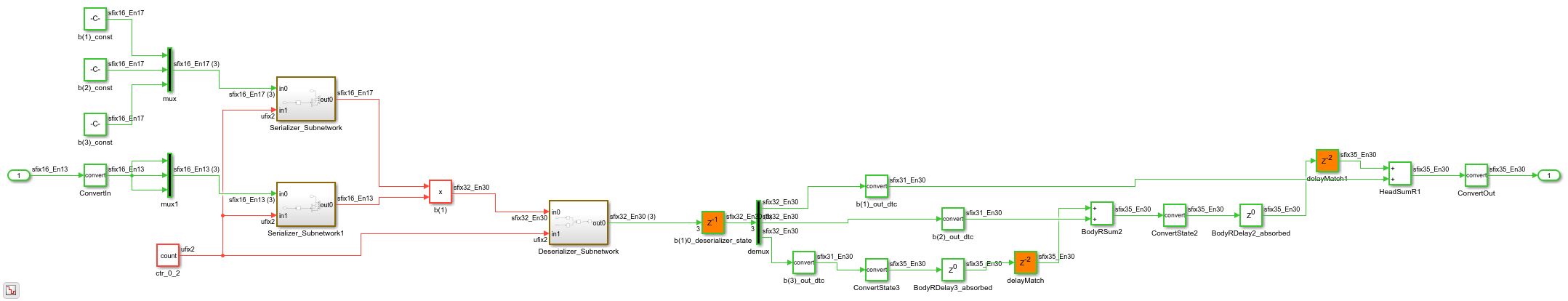

The code generation model reflects the sharing architecture. The inputs to the shared blocks are time-multiplexed over the shared resource at a faster rate (in this case 4x faster, shown in red). The outputs are then routed to the respective consumers at a slower rate (shown in green).

hdlset_param('sfir_fixed/symmetric_fir', 'SharingFactor', 4); hdlset_param('sfir_fixed', 'GenerateValidationModel', 'on'); makehdl('sfir_fixed/symmetric_fir'); open_system('gm_sfir_fixed/symmetric_fir'); set_param('gm_sfir_fixed', 'SimulationCommand', 'update');

### Working on the model <a href="matlab:open_system('sfir_fixed')">sfir_fixed</a>

### Generating HDL for <a href="matlab:open_system('sfir_fixed/symmetric_fir')">sfir_fixed/symmetric_fir</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('sfir_fixed', { 'HDL Code Generation' } )">sfir_fixed</a> for HDL code generation parameters.

### Running HDL checks on the model 'sfir_fixed'.

### Begin compilation of the model 'sfir_fixed'...

### Working on the model 'sfir_fixed'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Output port 2: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('sfir_fixed', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_sfir_fixed'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/sfir_fixed/gm_sfir_fixed.slx')">hdlsrc/sfir_fixed/gm_sfir_fixed.slx</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/sfir_fixed/gm_sfir_fixed_vnl')">gm_sfir_fixed_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'sfir_fixed'.

### MESSAGE: The design requires 4 times faster clock with respect to the base rate = 1.

### Begin VHDL Code Generation for 'symmetric_fir_tc'.

### Working on symmetric_fir_tc as hdlsrc/sfir_fixed/symmetric_fir_tc.vhd.

### Code Generation for 'symmetric_fir_tc' completed.

### Working on sfir_fixed/symmetric_fir as hdlsrc/sfir_fixed/symmetric_fir.vhd.

### Generating package file hdlsrc/sfir_fixed/symmetric_fir_pkg.vhd.

### Code Generation for 'sfir_fixed' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/sfir_fixed', '/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/sfir_fixed/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/sfir_fixed/symmetric_fir_report.html

### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

The sharing optimization is implemented by using time-division multiplexing. Simulink requires the outputs of the shared resource to be sampled at the predefined sample rate. HDL Coder overclocks the shared resource at a faster rate than the data rate. In the preceding example, the shared architecture, which includes the shared resources multiplexer-serializer at the inputs, and demultiplexer-deserializer at the outputs, operates at four times the rate of the input data, because the Sharingfactor is set to 4.

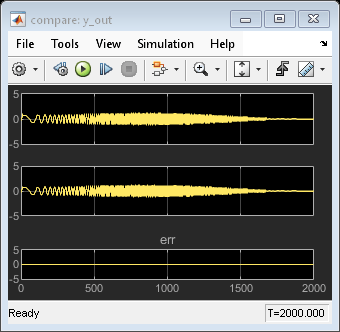

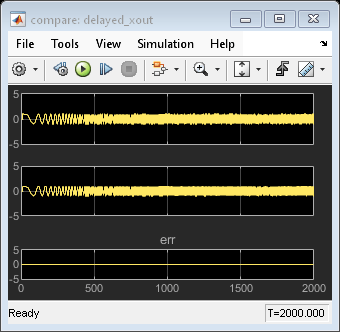

Delay Balancing and Functional Equivalence

The rate transitions that implement time-multiplexing in the resource sharing architecture introduce additional latency. To maintain functional equivalence, delay balancing inserts matching delays in parallel merging paths. The generated validation model enables you to verify functional equivalence by comparing the operation of the shared hardware architecture to the original model.

sim('gm_sfir_fixed_vnl'); open_system('gm_sfir_fixed_vnl/Compare/Assert_y_out/compare: y_out') open_system('gm_sfir_fixed_vnl/Compare/Assert_delayed_xout/compare: delayed_xout')

Control Multiplicative Oversampling Through SharingFactor

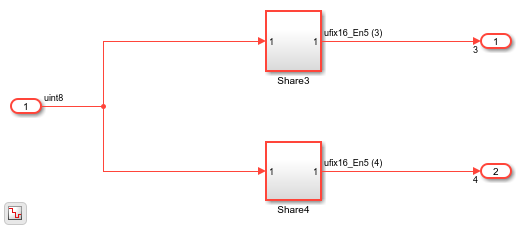

The net oversampling for the whole design is equivalent to the LCM of all SharingFactor values set on the model. Consider the example hdlcoder_uniform_oversampling.slx. It has two subsystems: subsystem Share3 has three gain blocks that can be shared and Share4 has four gain blocks that can be shared.

saved_warning_state = warning('off', 'hdlcoder:makehdl:DeprecateMaxOverSampling'); warning('off', 'hdlcoder:makehdl:DeprecateMaxComputationLatency'); load_system('hdlcoder_uniform_oversampling'); open_system('hdlcoder_uniform_oversampling/Subsystem'); set_param('hdlcoder_uniform_oversampling', 'SimulationCommand', 'update'); hdlsaveparams('hdlcoder_uniform_oversampling/Subsystem');

%% Set Model 'hdlcoder_uniform_oversampling' HDL parameters

hdlset_param('hdlcoder_uniform_oversampling', 'GenerateValidationModel', 'on');

hdlset_param('hdlcoder_uniform_oversampling', 'HDLSubsystem', 'hdlcoder_uniform_oversampling');

% Set SubSystem HDL parameters

hdlset_param('hdlcoder_uniform_oversampling/Subsystem/Share3', 'SharingFactor', 3);

% Set SubSystem HDL parameters

hdlset_param('hdlcoder_uniform_oversampling/Subsystem/Share4', 'SharingFactor', 4);

Share3 sets its SharingFactor to 3 and Share4 sets its SharingFactor to 4. HDL Coder applies local resource sharing to each subsystem and as a result, the HDL implementation requires LCM(3, 4)| = 12x oversampling. This oversampling is reported during HDL code generation.

makehdl('hdlcoder_uniform_oversampling/Subsystem');

### Working on the model <a href="matlab:open_system('hdlcoder_uniform_oversampling')">hdlcoder_uniform_oversampling</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_uniform_oversampling/Subsystem')">hdlcoder_uniform_oversampling/Subsystem</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_uniform_oversampling', { 'HDL Code Generation' } )">hdlcoder_uniform_oversampling</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_uniform_oversampling'.

### Begin compilation of the model 'hdlcoder_uniform_oversampling'...

### Working on the model 'hdlcoder_uniform_oversampling'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Output port 2: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_uniform_oversampling', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_uniform_oversampling'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling.slx')">hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling.slx</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling_vnl')">gm_hdlcoder_uniform_oversampling_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoder_uniform_oversampling'.

### MESSAGE: The design requires 12 times faster clock with respect to the base rate = 0.1.

### Begin VHDL Code Generation for 'Subsystem_tc'.

### Working on Subsystem_tc as hdlsrc/hdlcoder_uniform_oversampling/Subsystem_tc.vhd.

### Code Generation for 'Subsystem_tc' completed.

### Working on hdlcoder_uniform_oversampling/Subsystem/Share3 as hdlsrc/hdlcoder_uniform_oversampling/Share3.vhd.

### Working on hdlcoder_uniform_oversampling/Subsystem/Share4 as hdlsrc/hdlcoder_uniform_oversampling/Share4.vhd.

### Working on hdlcoder_uniform_oversampling/Subsystem as hdlsrc/hdlcoder_uniform_oversampling/Subsystem.vhd.

### Generating package file hdlsrc/hdlcoder_uniform_oversampling/Subsystem_pkg.vhd.

### Code Generation for 'hdlcoder_uniform_oversampling' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling', '/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling/Subsystem_report.html

### HDL check for 'hdlcoder_uniform_oversampling' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

One way to circumvent this multiplicative effect of oversampling is to set the SharingFactor of all subsystems to the available oversampling budget. In the above example, if the oversampling budget is only 4x, then set SharingFactor set to 4 for both Share3 and Share4. In this case, HDL Coder can share fewer resources than the SharingFactor and stay idle for the remaining cycles.

hdlset_param('hdlcoder_uniform_oversampling/Subsystem/Share3', 'SharingFactor', 4); makehdl('hdlcoder_uniform_oversampling/Subsystem');

### Working on the model <a href="matlab:open_system('hdlcoder_uniform_oversampling')">hdlcoder_uniform_oversampling</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_uniform_oversampling/Subsystem')">hdlcoder_uniform_oversampling/Subsystem</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_uniform_oversampling', { 'HDL Code Generation' } )">hdlcoder_uniform_oversampling</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_uniform_oversampling'.

### Begin compilation of the model 'hdlcoder_uniform_oversampling'...

### Working on the model 'hdlcoder_uniform_oversampling'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Output port 2: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_uniform_oversampling', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_uniform_oversampling'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling.slx')">hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling.slx</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling_vnl')">gm_hdlcoder_uniform_oversampling_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoder_uniform_oversampling'.

### MESSAGE: The design requires 4 times faster clock with respect to the base rate = 0.1.

### Begin VHDL Code Generation for 'Subsystem_tc'.

### Working on Subsystem_tc as hdlsrc/hdlcoder_uniform_oversampling/Subsystem_tc.vhd.

### Code Generation for 'Subsystem_tc' completed.

### Working on hdlcoder_uniform_oversampling/Subsystem/Share3 as hdlsrc/hdlcoder_uniform_oversampling/Share3.vhd.

### Working on hdlcoder_uniform_oversampling/Subsystem/Share4 as hdlsrc/hdlcoder_uniform_oversampling/Share4.vhd.

### Working on hdlcoder_uniform_oversampling/Subsystem as hdlsrc/hdlcoder_uniform_oversampling/Subsystem.vhd.

### Generating package file hdlsrc/hdlcoder_uniform_oversampling/Subsystem_pkg.vhd.

### Code Generation for 'hdlcoder_uniform_oversampling' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling', '/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling/Subsystem_report.html

### HDL check for 'hdlcoder_uniform_oversampling' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

The oversampling factor is now LCM(4,4) = 4. This value is the value reported during code generation. It is a best practice to set the SharingFactor values to the available oversampling budget. If your design contains fewer shareable resources than the SharingFactor value you specify, HDL Coder shares the shareable resources available and overclocks them by the SharingFactor value. If you want to apply resource sharing and other optimizations that use overclocking, such as streaming, or apply resource sharing in multiple nested subsystems, this general guideline might result in a higher oversampling factor.

Block Support, Atomic Subsystems, and Extensions

HDL Coder supports resource sharing of four block types: Product, Gain, Atomic Subsystem, and MATLAB Function. For MATLAB Function blocks, use the MATLAB Datapath architecture with fixed-point types. This architecture is the default setting for floating-point types. You can specify the HDL Architecture in the HDL Block Properties dialog box of the MATLAB Function block.

Sharing functionally equivalent Product and Gain blocks means that the multipliers in the HDL implementation are shared. Two Product blocks are functionally equivalent if:

The data types of their inputs and outputs are identical.

Their block parameter settings are identical.

Their HDL block properties are identical.

For a Gain block, functional equivalence additionally requires that the constant value and data types are also identical. If the gain constant data types are identical for two Gain blocks that have different gain constant values, HDL Coder can share them. Similarly, if a Gain block can be implemented as a Product block that has constant input, and it has the same data types as another Product block in the design, HDL Coder can share them.

The third block type, Atomic Subsystem, is useful for sharing functionally equivalent logic encapsulated inside atomic subsystems. Two atomic subsystems are functionally equivalent and can be shared if:

Their Simulink checksums are identical.

Their HDL block properties are identical.

Share Atomic Subsystems

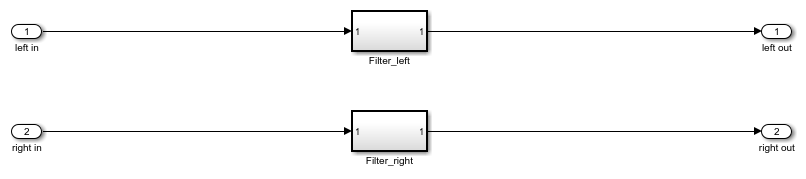

The following example demonstrates an audio filtering model that applies the same filter on the left and right channels. By default, HDL Coder generates two filter modules in hardware.

load_system('hdlcoder_audiofiltering'); open_system('hdlcoder_audiofiltering/Audio filter');

The filters on the two audio channels can be shared by specifying a SharingFactor value of 2 on the encompassing subsystem. This generates an architecture that uses only one filter, as shown below.

hdlset_param('hdlcoder_audiofiltering/Audio filter', 'SharingFactor', 2); makehdl('hdlcoder_audiofiltering/Audio filter'); open_system('gm_hdlcoder_audiofiltering/Audio filter'); set_param('gm_hdlcoder_audiofiltering', 'SimulationCommand', 'update');

### Working on the model <a href="matlab:open_system('hdlcoder_audiofiltering')">hdlcoder_audiofiltering</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_audiofiltering/Audio filter')">hdlcoder_audiofiltering/Audio filter</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_audiofiltering', { 'HDL Code Generation' } )">hdlcoder_audiofiltering</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_audiofiltering'.

### Begin compilation of the model 'hdlcoder_audiofiltering'...

### Working on the model 'hdlcoder_audiofiltering'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Output port 2: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_audiofiltering', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_audiofiltering'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx')">hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_audiofiltering'.

### MESSAGE: The design requires 2 times faster clock with respect to the base rate = 0.00012207.

### Begin VHDL Code Generation for 'Audio_filter_tc'.

### Working on Audio_filter_tc as hdlsrc/hdlcoder_audiofiltering/Audio_filter_tc.vhd.

### Code Generation for 'Audio_filter_tc' completed.

### Working on hdlcoder_audiofiltering/Audio filter/Filter_left as hdlsrc/hdlcoder_audiofiltering/Filter_left.vhd.

### Working on hdlcoder_audiofiltering/Audio filter as hdlsrc/hdlcoder_audiofiltering/Audio_filter.vhd.

### Generating package file hdlsrc/hdlcoder_audiofiltering/Audio_filter_pkg.vhd.

### Code Generation for 'hdlcoder_audiofiltering' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering', '/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering/Audio_filter_report.html

### HDL check for 'hdlcoder_audiofiltering' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

Opportunities to Resource Share Across Hierarchies

Because SharingFactor is a subsystem-level parameter, different subsystems at different levels of the hierarchy can specify different sharing values. In the audio filter example, the filters on each channel use three gain blocks respectively.

open_system('hdlcoder_audiofiltering/Audio filter/Filter_left');

Share Resources at Higher Level of Hierarchy

You can specify a SharingFactor value of 2 at the top-level of the DUT to share the filters on the two channels. You can specify a SharingFactor value of 3 on each of the filter subsystems to enable sharing of the three gain blocks in each channel. When HDL code is now generated, the left and right filters have been shared. Only one filter is at the top-level of the hierarchy.

hdlset_param('hdlcoder_audiofiltering/Audio filter', 'SharingFactor', 2); hdlset_param('hdlcoder_audiofiltering/Audio filter/Filter_left', 'SharingFactor', 3); hdlset_param('hdlcoder_audiofiltering/Audio filter/Filter_right', 'SharingFactor', 3); makehdl('hdlcoder_audiofiltering/Audio filter'); open_system('gm_hdlcoder_audiofiltering/Audio filter'); set_param('gm_hdlcoder_audiofiltering', 'SimulationCommand', 'update');

### Working on the model <a href="matlab:open_system('hdlcoder_audiofiltering')">hdlcoder_audiofiltering</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_audiofiltering/Audio filter')">hdlcoder_audiofiltering/Audio filter</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_audiofiltering', { 'HDL Code Generation' } )">hdlcoder_audiofiltering</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_audiofiltering'.

### Begin compilation of the model 'hdlcoder_audiofiltering'...

### Working on the model 'hdlcoder_audiofiltering'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 2 cycles.

### Output port 2: 2 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_audiofiltering', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_audiofiltering'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx')">hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_audiofiltering'.

### MESSAGE: The design requires 6 times faster clock with respect to the base rate = 0.00012207.

### Begin VHDL Code Generation for 'Audio_filter_tc'.

### Working on Audio_filter_tc as hdlsrc/hdlcoder_audiofiltering/Audio_filter_tc.vhd.

### Code Generation for 'Audio_filter_tc' completed.

### Working on hdlcoder_audiofiltering/Audio filter/Filter_left as hdlsrc/hdlcoder_audiofiltering/Filter_left.vhd.

### Working on hdlcoder_audiofiltering/Audio filter as hdlsrc/hdlcoder_audiofiltering/Audio_filter.vhd.

### Generating package file hdlsrc/hdlcoder_audiofiltering/Audio_filter_pkg.vhd.

### Code Generation for 'hdlcoder_audiofiltering' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering', '/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering/Audio_filter_report.html

### HDL check for 'hdlcoder_audiofiltering' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

Share Resources at Lower Level of Hierarchy

The three gain blocks in the lower level of the hierarchy (within the filter subsystem) have also been shared. You have reduced the resource usage from six multipliers to just one.

open_system('gm_hdlcoder_audiofiltering/Audio filter/Filter_left'); set_param('gm_hdlcoder_audiofiltering', 'SimulationCommand', 'update');

Combine Optimizations and Sharing

Resource sharing can be combined with other optimizations, such as the streaming optimization.

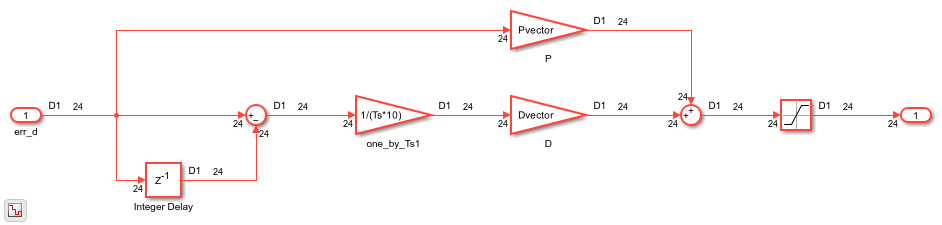

Consider this model. it contains a 24-element vector datapath and three vector gain blocks, which map to 72 multipliers, by default. Streaming can scalarize the vector datapath while sharing can share the three Gain blocks.

load_system('hdl_areaopt1'); open_system('hdl_areaopt1/Controller'); set_param('hdl_areaopt1', 'SimulationCommand', 'update');

Streaming and Sharing to Reduce Design to Use One Multiplier

To invoke both optimizations, set StreamingFactor to 24 and SharingFactor to 3. The former reduces the number of multipliers from 72 to 3. The latter reduces the 3 scalar multipliers to 1.

hdlset_param('hdl_areaopt1/Controller', 'StreamingFactor', 24); hdlset_param('hdl_areaopt1/Controller', 'SharingFactor', 3); makehdl('hdl_areaopt1/Controller'); open_system('gm_hdl_areaopt1/Controller'); set_param('gm_hdl_areaopt1', 'SimulationCommand', 'update');

### Working on the model <a href="matlab:open_system('hdl_areaopt1')">hdl_areaopt1</a>

### Generating HDL for <a href="matlab:open_system('hdl_areaopt1/Controller')">hdl_areaopt1/Controller</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdl_areaopt1', { 'HDL Code Generation' } )">hdl_areaopt1</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdl_areaopt1'.

### Begin compilation of the model 'hdl_areaopt1'...

### Working on the model 'hdl_areaopt1'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 2 cycles.

### Working on... <a href="matlab:configset.internal.open('hdl_areaopt1', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdl_areaopt1'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdl_areaopt1/gm_hdl_areaopt1.slx')">hdlsrc/hdl_areaopt1/gm_hdl_areaopt1.slx</a>

### Begin VHDL Code Generation for 'hdl_areaopt1'.

### MESSAGE: The design requires 72 times faster clock with respect to the base rate = 2.

### Begin VHDL Code Generation for 'Controller_tc'.

### Working on Controller_tc as hdlsrc/hdl_areaopt1/Controller_tc.vhd.

### Code Generation for 'Controller_tc' completed.

### Working on hdl_areaopt1/Controller as hdlsrc/hdl_areaopt1/Controller.vhd.

### Generating package file hdlsrc/hdl_areaopt1/Controller_pkg.vhd.

### Code Generation for 'hdl_areaopt1' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdl_areaopt1', '/tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdl_areaopt1/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3233028_1587614/tpe47fa6f0/hdlcoder-ex96854632/hdlsrc/hdl_areaopt1/Controller_report.html

### HDL check for 'hdl_areaopt1' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.