Iteratively Meet Timing Requirements Using Multicycle Path Constraints for Cadence Genus

This example shows how to apply multicycle path (MCP) constraints in your design to meet timing requirements when synthesizing with the Cadence® Genus synthesis tool. This example uses the post-synthesis timing analysis results from a Cadence Genus synthesis tool for an ASIC device to illustrate the impact of enabled multicycle path constraints. HDL Coder™ generates constraint files in SDC format for use with Cadence Genus.

Requirements

HDL Coder™

Red Hat® Linux release 8.9

Cadence Genus version 21.18

Set Synthesis Tool Path

Set the path to the Cadence Genus synthesis tool path by using the hdlsetuptoolpath command:

hdlsetuptoolpath('ToolName','Cadence Genus','ToolPath', installation_path);

installation_path is the path to the Cadence Genus synthesis tool version supported in the current release. See HDL Language Support and Supported Third-Party Tools and Hardware.

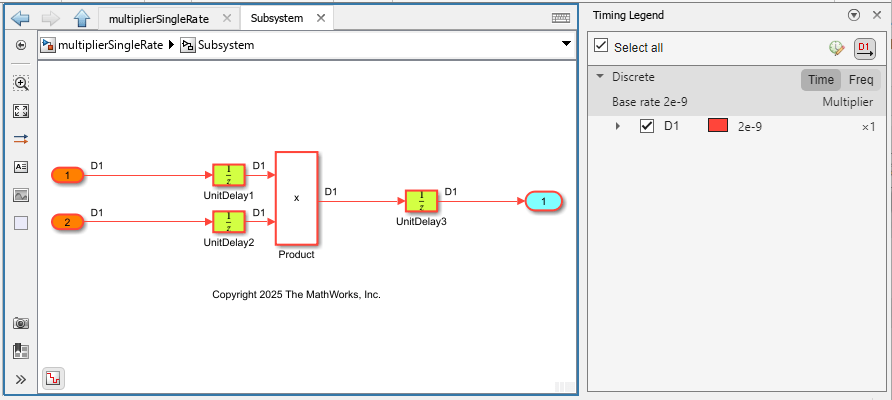

Generate HDL Code and Synthesize Without Using MCP Constraints

Open the example multiplierSingleRate.slx model. To open this model, in the MATLAB command prompt, enter:

load_system('multiplierSingleRate.slx'); open_system('multiplierSingleRate/MCPSubsystem');

This model is compatible for HDL code generation. To generate HDL code and synthesize it without using MCP constraints, follow these steps:

In the Apps tab, click HDL Coder. Then, in the HDL Code tab, click Workflow Advisor.

In he HDL Workflow Advisor, in the 1.1. Set Target Device and Synthesis Tool task, set Target workflow to

Generic ASIC/FPGAand Synthesis tool toCadence Genus.Then, click Run This Task.In the 1.2. Set Target Frequency task, set Target Frequency (MHz) to

500.In the 3.1. Set HDL Options task, click HDL Code Generation Settings. In the Configuration Parameters dialog box, navigate to HDL Code Generation > Optimization. In the Multicycle Path Constraints section clear the Enable-based constraints parameter. Click OK.

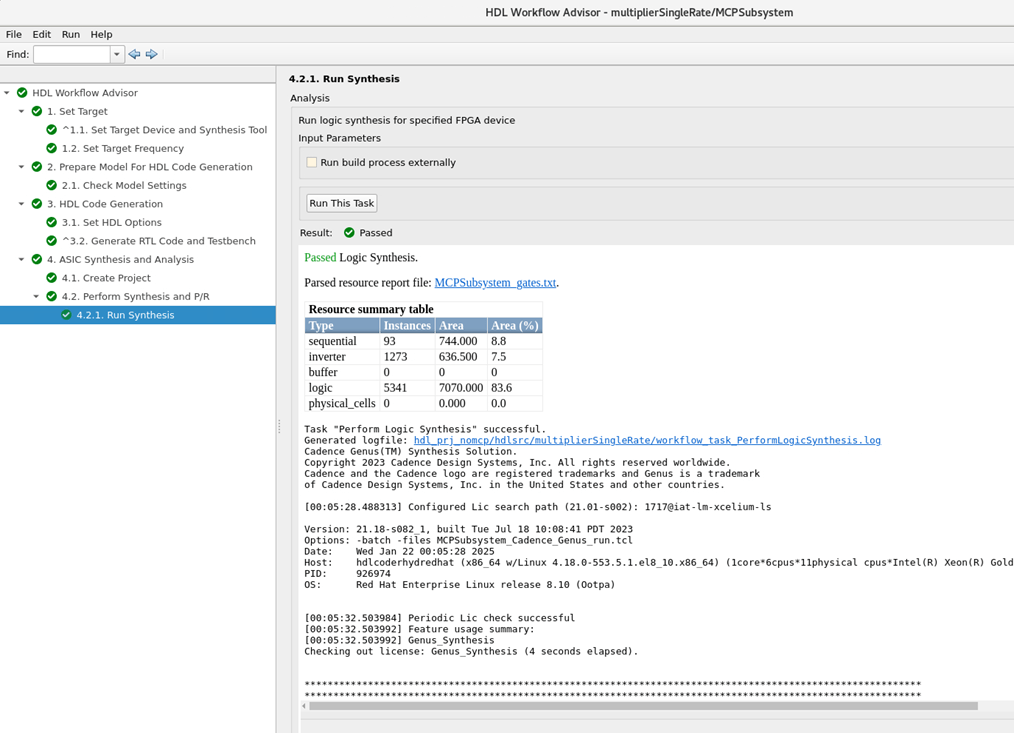

In the HDL Workflow Advisor, in the 4.1. Create Project task, set Synthesis workflow to

Default.To perform synthesis, in the 4.2.1. Run Synthesis task, click Run This Task. The Result pane includes a the link to the parsed resource report file, the log file and the resource summary table.

You can view the timing report file, MCPSubsystem_timing.txt, located in the hdlsrc folder in the project hierarchy. The file indicates that the generated HDL code fails to meet the 500MHz timing requirement for the clock. The timing requirement is 2000 ps, or 1/500MHz, and a negative slack of -3470 ps indicates a violation of this requirement.

============================================================

Generated by: Genus(TM) Synthesis Solution 21.18-s082_1

Generated on: Jan 21 2025 07:19:16 am

Module: MCPSubsystem

Operating conditions: typical_case (balanced_tree)

Wireload mode: enclosed

Area mode: timing library

============================================================

Path 1: VIOLATED (-3470 ps) Setup Check with Pin Unit_Delay2_out1_reg[30]/CK->D

Group: MWCLK

Startpoint: (R) Unit_Delay1_out1_reg[19]/CK

Clock: (R) MWCLK

Endpoint: (R) Unit_Delay2_out1_reg[30]/D

Clock: (R) MWCLK

Capture Launch

Clock Edge:+ 2000 0

Src Latency:+ 0 0

Net Latency:+ 0 (I) 0 (I)

Arrival:= 2000 0

Setup:- 100

Required Time:= 1900

Launch Clock:- 0

Data Path:- 5370

Slack:= -3470

#----------------------------------------------------------------------------------------------------

# Timing Point Flags Arc Edge Cell Fanout Load Trans Delay Arrival Instance

# (fF) (ps) (ps) (ps) Location

#----------------------------------------------------------------------------------------------------

Unit_Delay1_out1_reg[19]/CK - - R (arrival) 93 - 0 0 0 (-,-)

Unit_Delay1_out1_reg[19]/Q - CK->Q F flopdrs 2 41.0 21 149 149 (-,-)

fopt57221/Y - A->Y R inv1 2 31.0 19 87 236 (-,-)

mul_97_39_g56502_0/Y - A->Y R xor2 1 10.7 54 142 377 (-,-)

mul_97_39_g55589/Y - B->Y F nand2 2 41.0 53 132 510 (-,-)

fopt57189/Y - A->Y R inv1 1 10.7 15 85 594 (-,-)

mul_97_39_g55199/Y - B->Y F nand2 1 10.7 45 121 716 (-,-)

mul_97_39_g54666/Y - B->Y R nand2 3 36.3 51 125 841 (-,-)

mul_97_39_g56994/Y - A->Y F nor2 1 20.7 57 137 978 (-,-)

mul_97_39_g56993/Y - A->Y R inv1 1 10.7 15 85 1063 (-,-)

mul_97_39_g53297/Y - B->Y F nand2 1 10.7 45 121 1184 (-,-)

mul_97_39_g53062/Y - B->Y R nand2 2 26.0 48 123 1307 (-,-)

mul_97_39_g52528/Y - B->Y R xor2 1 15.7 56 146 1452 (-,-)

mul_97_39_g52104/Y - B->Y R xor2 2 31.0 60 150 1602 (-,-)

mul_97_39_g51723/Y - A->Y F nand2 1 10.7 45 125 1728 (-,-)

mul_97_39_g51569/Y - B->Y R nand2 1 10.7 45 119 1846 (-,-)

mul_97_39_g51514/Y - B->Y F nand2 2 36.0 51 130 1977 (-,-)

mul_97_39_g51459/Y - A->Y R inv1 1 10.7 15 84 2061 (-,-)

mul_97_39_g51169__5107/Y - B->Y F nor2 1 10.7 55 131 2192 (-,-)

mul_97_39_g51080__8246/Y - B->Y R nor2 2 31.0 60 140 2332 (-,-)

mul_97_39_g50956__5477/Y - B->Y F nand2 1 10.7 45 125 2458 (-,-)

mul_97_39_g50864__9315/Y - B->Y R nand2 1 10.7 45 119 2576 (-,-)

mul_97_39_g50855__5115/Y - B->Y F nand2 3 46.3 54 133 2709 (-,-)

mul_97_39_g50758__9315/Y - B->Y R nor2 1 10.7 55 135 2844 (-,-)

mul_97_39_g50700__5107/Y - A->Y F nor2 1 10.7 55 135 2979 (-,-)

mul_97_39_g50655__2346/Y - A->Y R nor2 2 21.0 58 137 3116 (-,-)

mul_97_39_g50527__5477/Y - A->Y F nand2 2 31.0 50 130 3246 (-,-)

mul_97_39_g50477__9315/Y - A->Y R nand2 2 21.0 48 122 3368 (-,-)

mul_97_39_g50446_0/Y - A->Y F nand2 1 10.7 45 124 3492 (-,-)

mul_97_39_g50434__9315/Y - A->Y R nand2 2 21.0 48 122 3614 (-,-)

mul_97_39_g50411_0/Y - A->Y F nand2 1 10.7 45 124 3738 (-,-)

mul_97_39_g50391__1881/Y - A->Y R nand2 1 10.7 45 119 3857 (-,-)

mul_97_39_g50382__3680/Y - A->Y F nand2 2 21.0 47 126 3983 (-,-)

mul_97_39_g50370_0/Y - B->Y R nor2 1 10.7 55 134 4117 (-,-)

mul_97_39_g50363__9315/Y - A->Y F nor2 2 21.0 58 137 4255 (-,-)

mul_97_39_g50358_0/Y - A->Y R nor2 2 31.0 60 140 4395 (-,-)

fopt57159/Y - A->Y F inv1 1 10.7 15 85 4480 (-,-)

mul_97_39_g50329__2883/Y - A->Y R nand2 1 10.7 44 116 4596 (-,-)

mul_97_39_g50309__6260/Y - B->Y F nand2 1 10.7 45 124 4720 (-,-)

mul_97_39_g50279__6260/Y - B->Y R nor2 1 10.7 55 134 4854 (-,-)

mul_97_39_g50263__6131/Y - B->Y F nand2 1 15.7 46 126 4980 (-,-)

mul_97_39_g50253__8428/Y - B->Y R xor2 1 10.7 55 144 5124 (-,-)

g942__2346/Y - B->Y F nand2 1 10.7 45 125 5249 (-,-)

g788__2802/Y - A->Y R nand2 1 20.7 47 121 5370 (-,-)

Unit_Delay2_out1_reg[30]/D <<< - R flopdrs 1 - - 0 5370 (-,-)

#----------------------------------------------------------------------------------------------------

Generate HDL Code and Synthesize with MCP Constraints

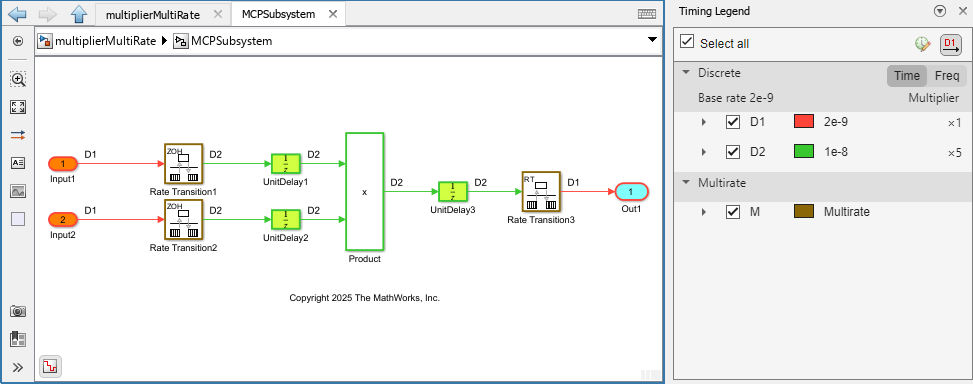

To meet the timing requirements, use multicycle path constraints. The multiplierMultiRate.slx model is a modified version of the multiplierSingleRate.slx model and includes a Product block surrounded by delays that operate at different data rates. This design can tolerate multiple clock cycles as the data propagates through it. HDL Coder requires multicycle regions to be surrounded by slow-clocked elements, such as delays, so that the constraints can define the paths among them as multicycle paths. When you enable Enable-based constraints, HDL Coder generates an additional file during HDL code generation.

load_system('multiplierMultiRate.slx') open_system('multiplierMultiRate/MCPSubsystem');

To generate HDL code for the Simulink model and synthesize it using MCP constraints, follow these steps in the HDL Workflow Advisor:

In 3.1. Set HDL Options task, click HDL Code Generation Settings. In the Configuration Parameters dialog box, navigate to HDL Code Generation > Optimization. In the Multicycle Path Constraints section enable the Enable-based constraints parameter. Click OK.

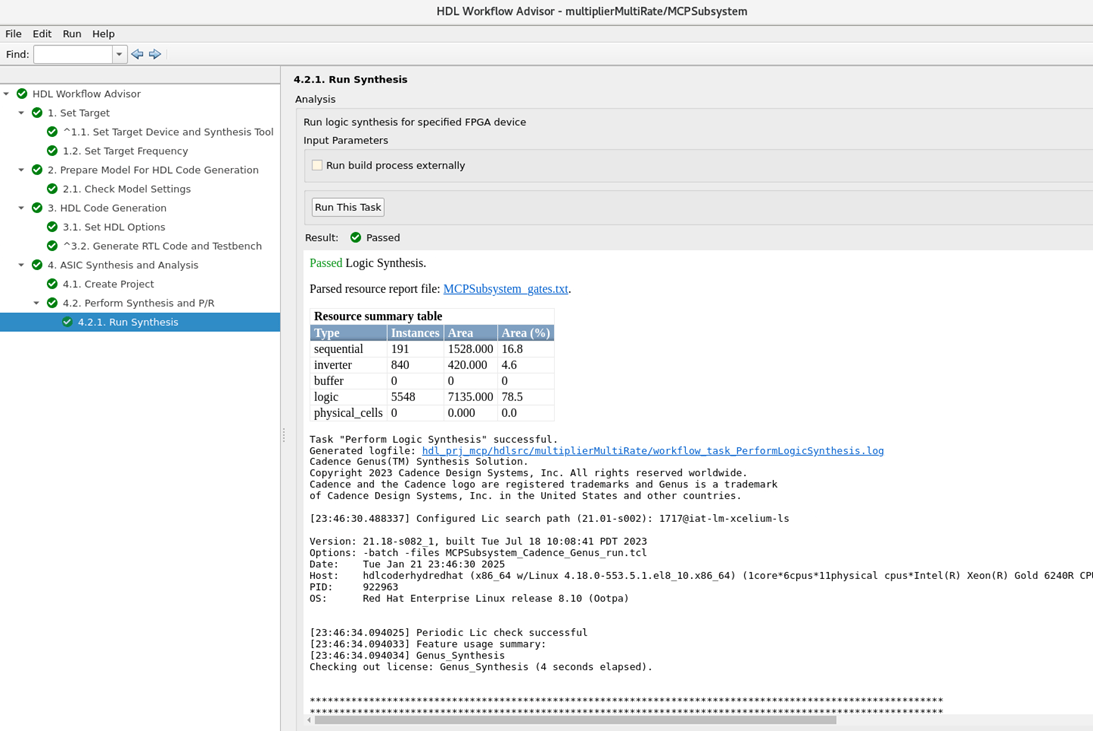

In the HDL Workflow Advisor, in the 4.1. Create Project task, set Synthesis workflow to

Default.To perform synthesis, in the 4.2.1. Run Synthesis task, click Run This Task. The Result pane includes a link to the parsed resource report file, the log file and the resource summary table.

View these SDC constraints by opening the MCP_Subsystem_constraints.sdc file in the hdlsrc folder in the main project hierarchy.

# Multicycle constraints for clock enable: MCPSubsystem_tc.u1_d5_o0 set MCPnet0 [get_db hnets .name *u_MCPSubsystem_tc/phase_0] set MCPreg0 [get_cells -of [all_fanout -flat -endpoints_only -from $MCPnet0]] set_multicycle_path 5 -setup -from $MCPreg0 -to $MCPreg0 set_multicycle_path 4 -hold -from $MCPreg0 -to $MCPreg0 # Multicycle constraints for clock enable: MCPSubsystem_tc.u1_d5_o1 set MCPnet1 [get_db hnets .name *u_MCPSubsystem_tc/phase_1] set MCPreg1 [get_cells -of [all_fanout -flat -endpoints_only -from $MCPnet1]] set_multicycle_path 5 -setup -from $MCPreg1 -to $MCPreg1 set_multicycle_path 4 -hold -from $MCPreg1 -to $MCPreg1

The HDL Workflow Advisor integrates the MCPSubsystem_constraints.sdc file in the Synthesis TCL. You can view a copy of this synthesis TCL file by opening the TCL file in the hdlsrc folder in the main project hierarchy.

# HDL Coder Downstream Integration Tcl Script

set myTool "Cadence Genus 21.18"

set myProject ""

set myProjectFile ""

set myTopLevelEntity "MCPSubsystem"

# Set project properties

puts "### Set $myTool project properties"

set_db library tutorial.lib

set_db syn_global_effort low

set_db super_thread_servers "localhost"

set_db st_launch_wait_time 1

# Add HDL source files

puts "### Update $myTool project with HDL source files"

read_hdl -language vhdl ../hdlsrc/multiplierMultiRate/MCPSubsystem_tc.vhd

read_hdl -language vhdl ../hdlsrc/multiplierMultiRate/MCPSubsystem.vhd

elaborate ${myTopLevelEntity}

source ../hdlsrc/multiplierMultiRate/MCPSubsystem_constraints.sdc

# Running Synthesis

puts "### Running Synthesis in $myTool ..."

create_clock -name MWCLK -period 2 [get_ports clk]

syn_generic

syn_map

report_timing > ./reports/MCPSubsystem_timing.txt

report_area -min_count 100 -detail > ./reports/MCPSubsystem_area.txt

report_qor > ./reports/MCPSubsystem_qor.txt

report_gates > ./reports/MCPSubsystem_gates.txt

exit

puts "### Synthesis Complete."

Open the MCP_Subsystem_timing.txt file to view the timing report for the synthesized HDL code. A positive slack of 675 ps indicates there are no timing violations and the design meets the required clock frequency.

============================================================

Generated by: Genus(TM) Synthesis Solution 21.18-s082_1

Generated on: Jan 21 2025 07:26:53 am

Module: MCPSubsystem

Operating conditions: typical_case (balanced_tree)

Wireload mode: enclosed

Area mode: timing library

============================================================

Path 1: MET (675 ps) Setup Check with Pin UnitDelay_5_out1_reg[30]/CK->D

Group: MWCLK

Startpoint: (R) u_MCPSubsystem_tc/phase_0_reg/CK

Clock: (R) MWCLK

Endpoint: (F) UnitDelay_5_out1_reg[30]/D

Clock: (R) MWCLK

Capture Launch

Clock Edge:+ 2000 0

Src Latency:+ 0 0

Net Latency:+ 0 (I) 0 (I)

Arrival:= 2000 0

Setup:- 100

Required Time:= 1900

Launch Clock:- 0

Data Path:- 1225

Slack:= 675

#-----------------------------------------------------------------------------------------------------------

# Timing Point Flags Arc Edge Cell Fanout Load Trans Delay Arrival Instance

# (fF) (ps) (ps) (ps) Location

#-----------------------------------------------------------------------------------------------------------

u_MCPSubsystem_tc/phase_0_reg/CK - - R (arrival) 191 - 0 0 0 (-,-)

u_MCPSubsystem_tc/phase_0_reg/Q - CK->Q R flopdrs 2 20.6 16 148 148 (-,-)

u_MCPSubsystem_tc/g189__5107/Y - B->Y F nand2 1 20.4 46 124 271 (-,-)

u_MCPSubsystem_tc/g188/Y - A->Y R inv1 1 25.7 18 88 359 (-,-)

g199/Y - A->Y R buf1 125 1297.9 203 325 684 (-,-)

g944/Y - A->Y F inv1 124 1277.6 285 283 967 (-,-)

g632__4733/Y - B->Y R nand2 1 10.7 49 131 1098 (-,-)

g385__2346/Y - B->Y F nand2 1 20.7 47 127 1225 (-,-)

UnitDelay_5_out1_reg[30]/D - - F flopdrs 1 - - 0 1225 (-,-)

#-----------------------------------------------------------------------------------------------------------