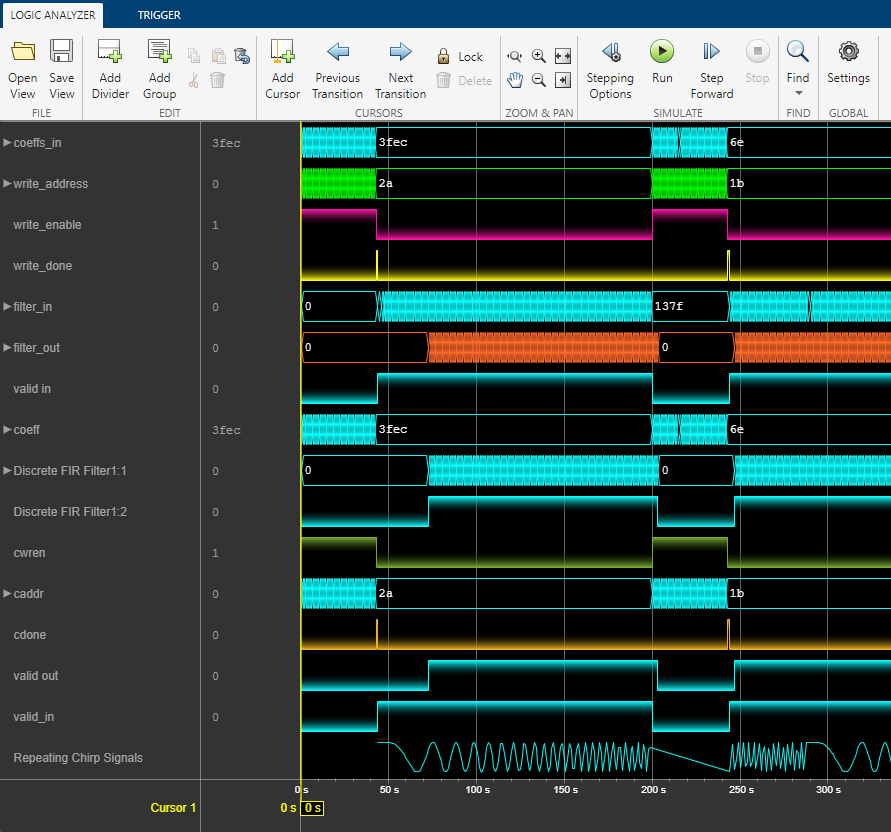

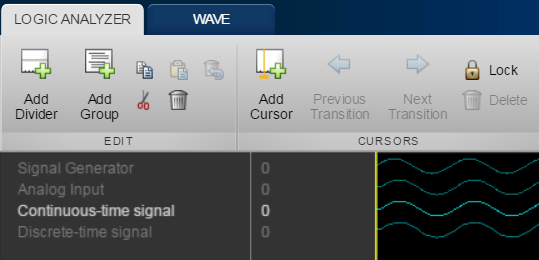

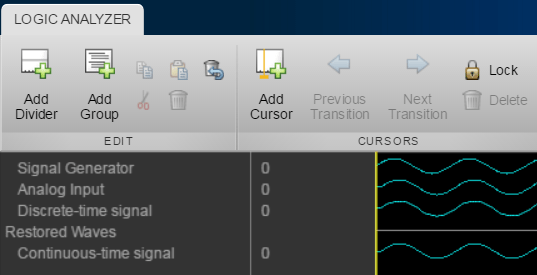

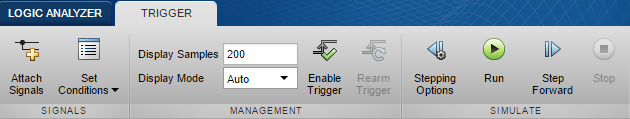

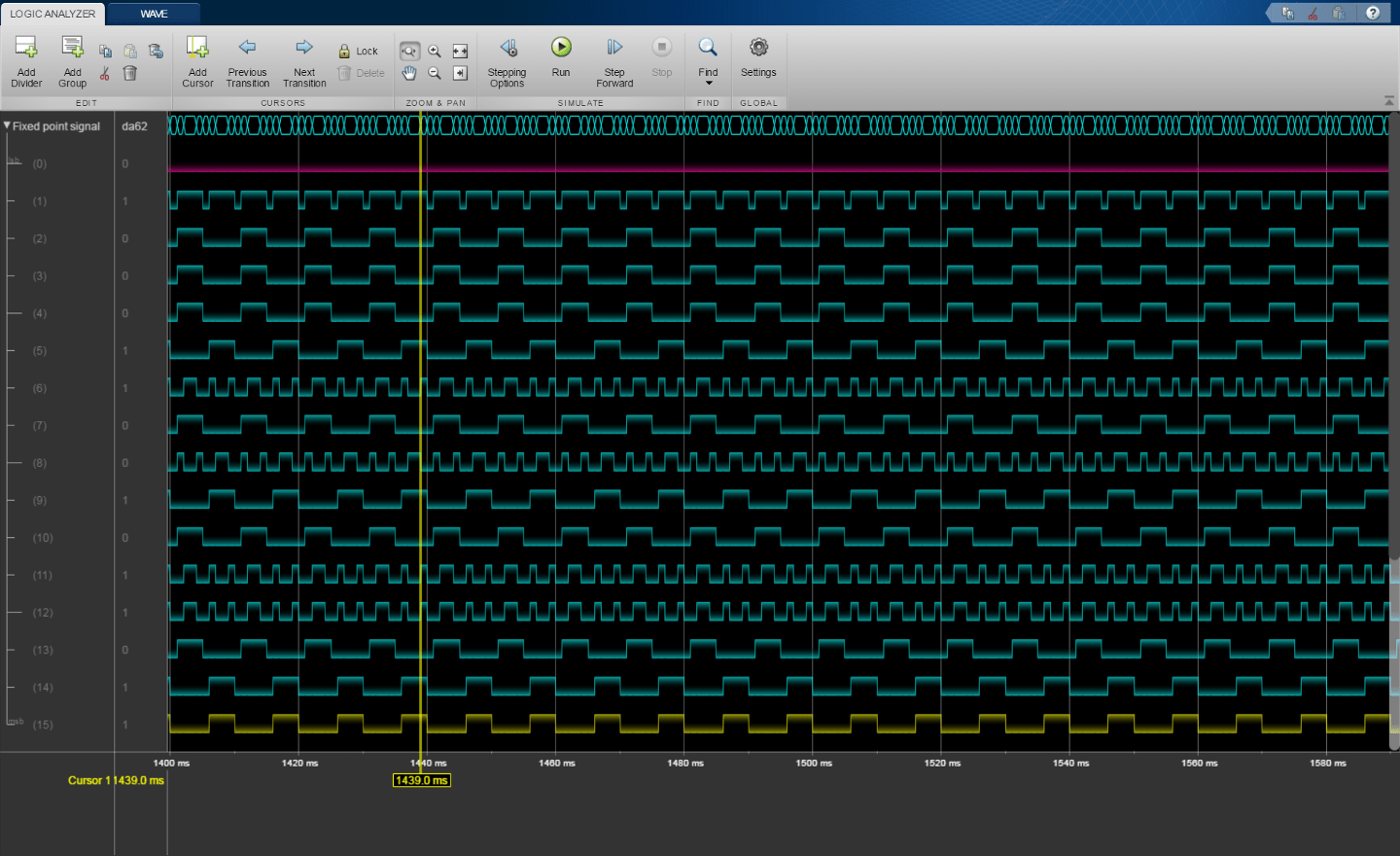

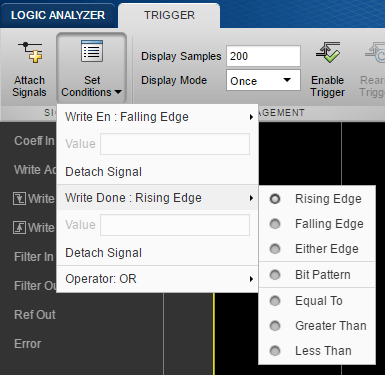

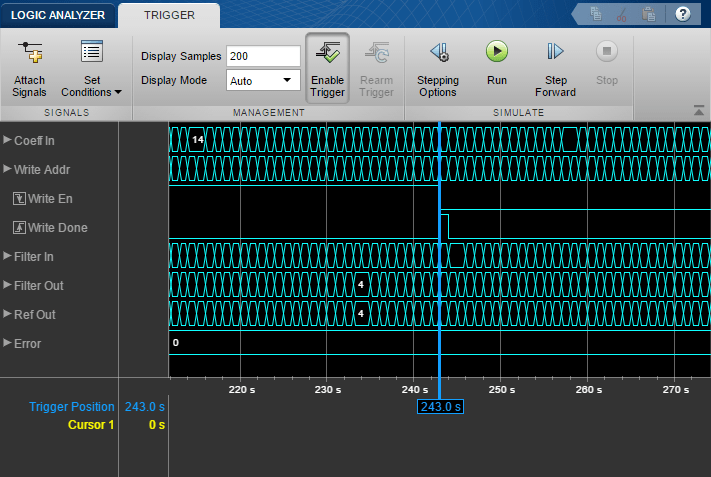

Logic Analyzer

Visualize, measure, and analyze transitions and states over time

Open the Logic Analyzer App

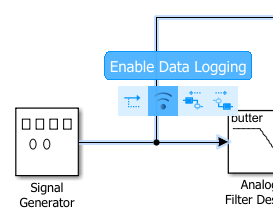

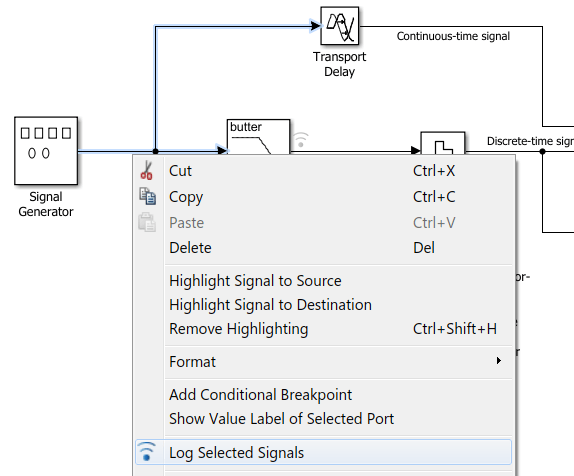

On the Simulation tab in the Simulink Editor menu, click the Logic Analyzer app button. If the button is not displayed, expand the Review Results gallery and you will find the Logic Analyzer app under Signal Logging Results. Your most recent choice for data visualization is saved across Simulink sessions.

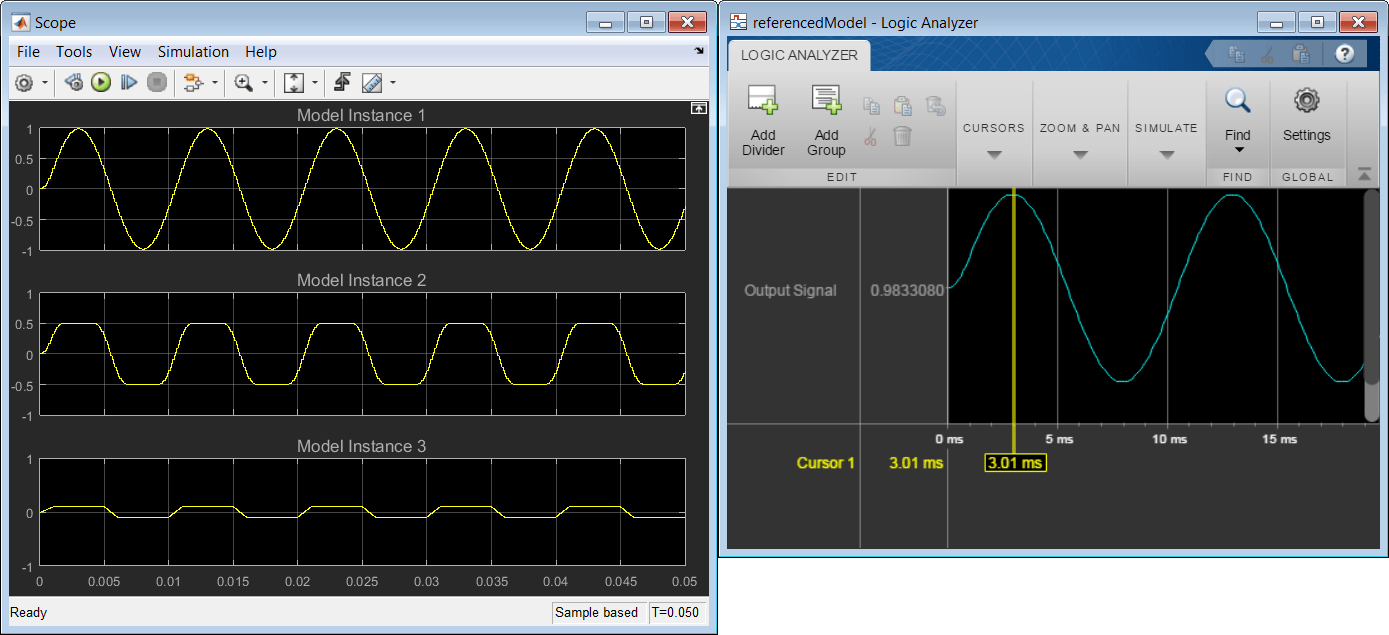

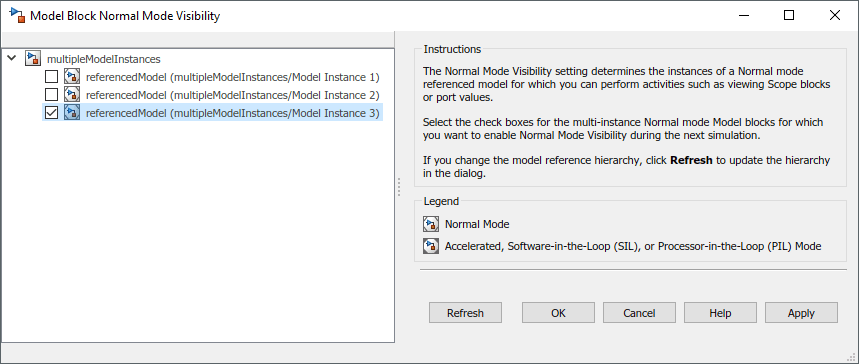

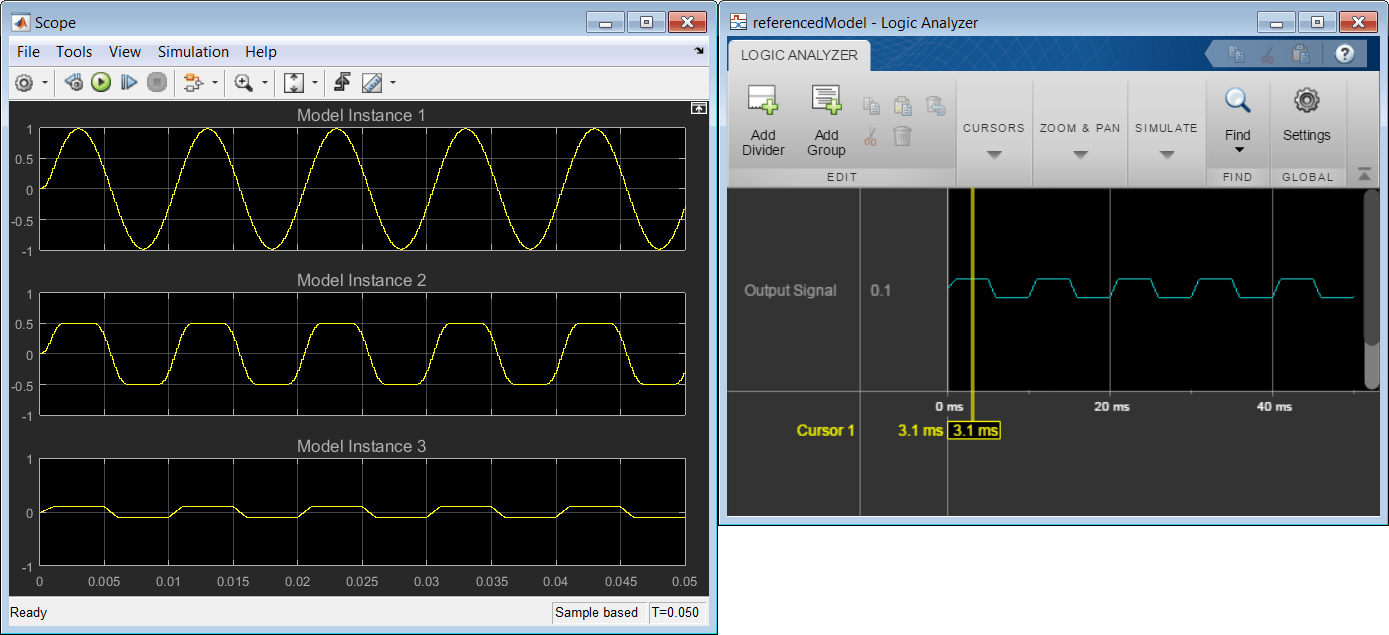

To visualize referenced models, you must open the Logic Analyzer from the referenced model. You should see the name of the referenced model in the Logic Analyzer toolbar.

Examples

Related Examples

- Inspect and Measure Transitions Using the Logic Analyzer

- Visualizing Multiple Signals Using Logic Analyzer

- Partly Serial Systolic FIR Filter Implementation (DSP HDL Toolbox)

- Fully Parallel Systolic FIR Filter Implementation (DSP HDL Toolbox)

- Configure Logic Analyzer

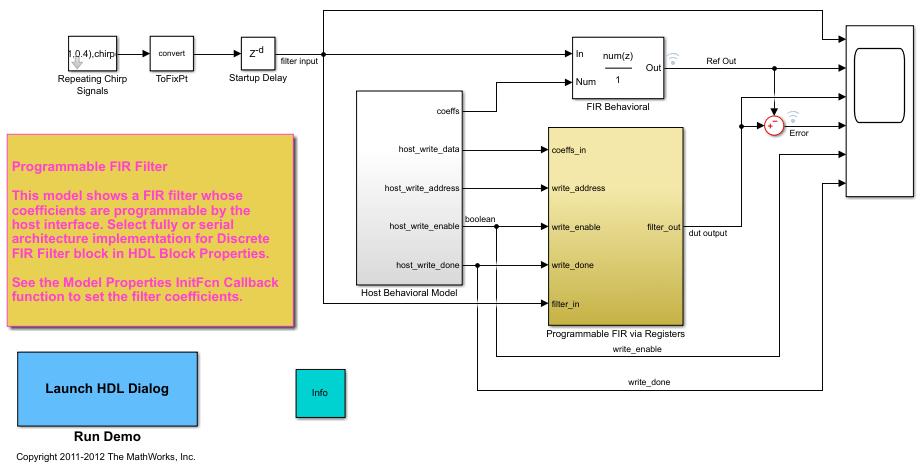

- Programmable FIR Filter for FPGA (HDL Coder)

- Log Simulation Output for States and Data (Stateflow)

- View Stateflow States in the Logic Analyzer (Stateflow)

Limitations

Logging Settings

If you enable the configuration parameter Log Dataset data to file (Simulink), you cannot stream logged data to the Logic Analyzer.

Signals marked for logging using

Simulink.sdi.markSignalForStreaming(Simulink) or visualized with a Dashboard Scope (Simulink) do not appear on the Logic Analyzer.You cannot visualize Data Store Memory (Simulink) block signals in the Logic Analyzer if you set the Log data store data parameter to on.

Input Signal Limitations

Signals marked for logging for the Logic Analyzer must have fewer than 8000 samples per simulation step.

The Logic Analyzer does not support frame-based processing.

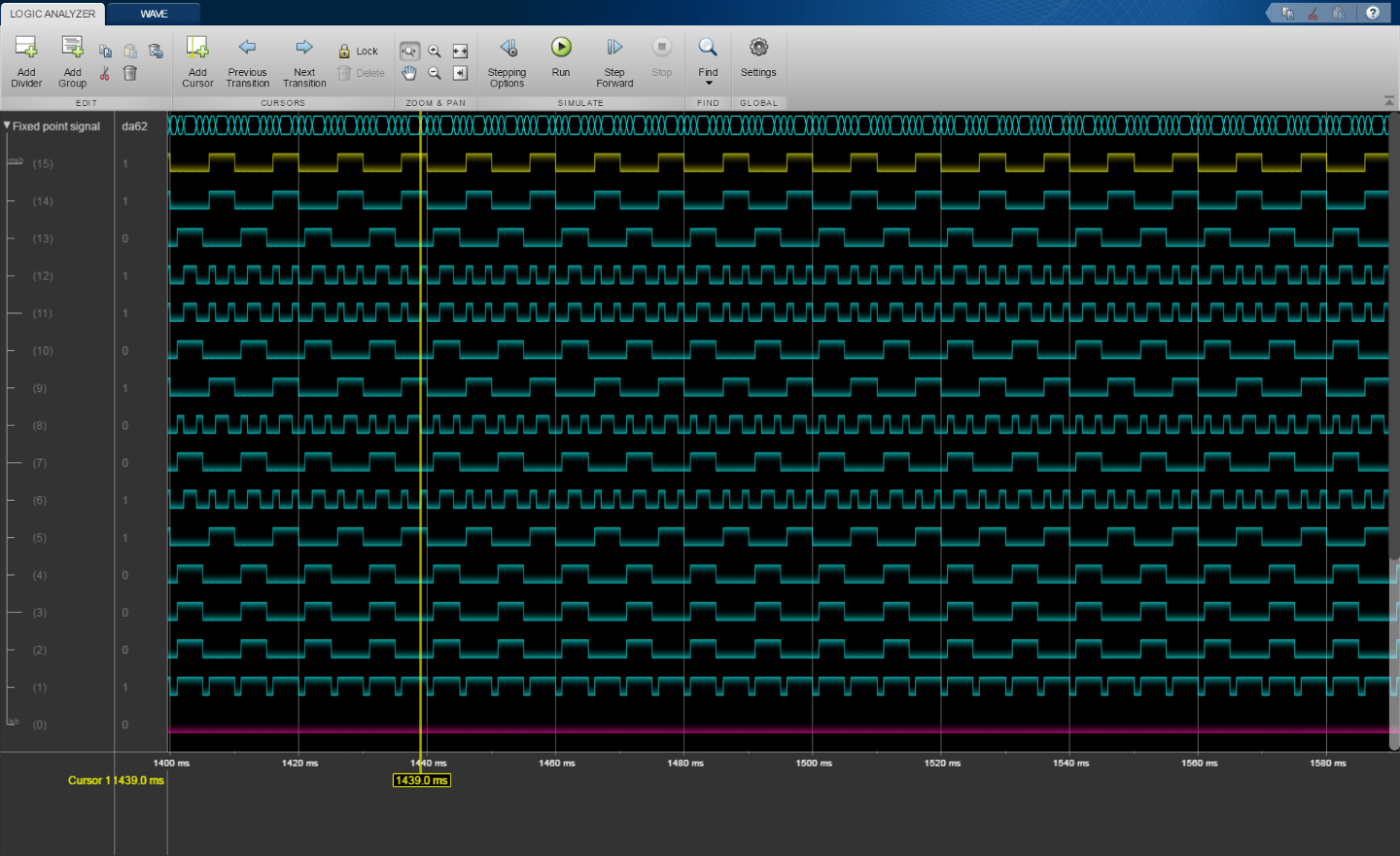

For 64-bit integers and fixed-point numbers greater than 53 bits, if the numbers are greater than the maximum value of double precision, the transitions between numbers might not display correctly.

You may see performance degradation in the Logic Analyzer for large matrices (greater than 500 elements) and buses with more than 1000 signals.

The Logic Analyzer app does not support Stateflow® data output.

The Logic Analyzer app does not display any waveform for

InfandNaNvalues.

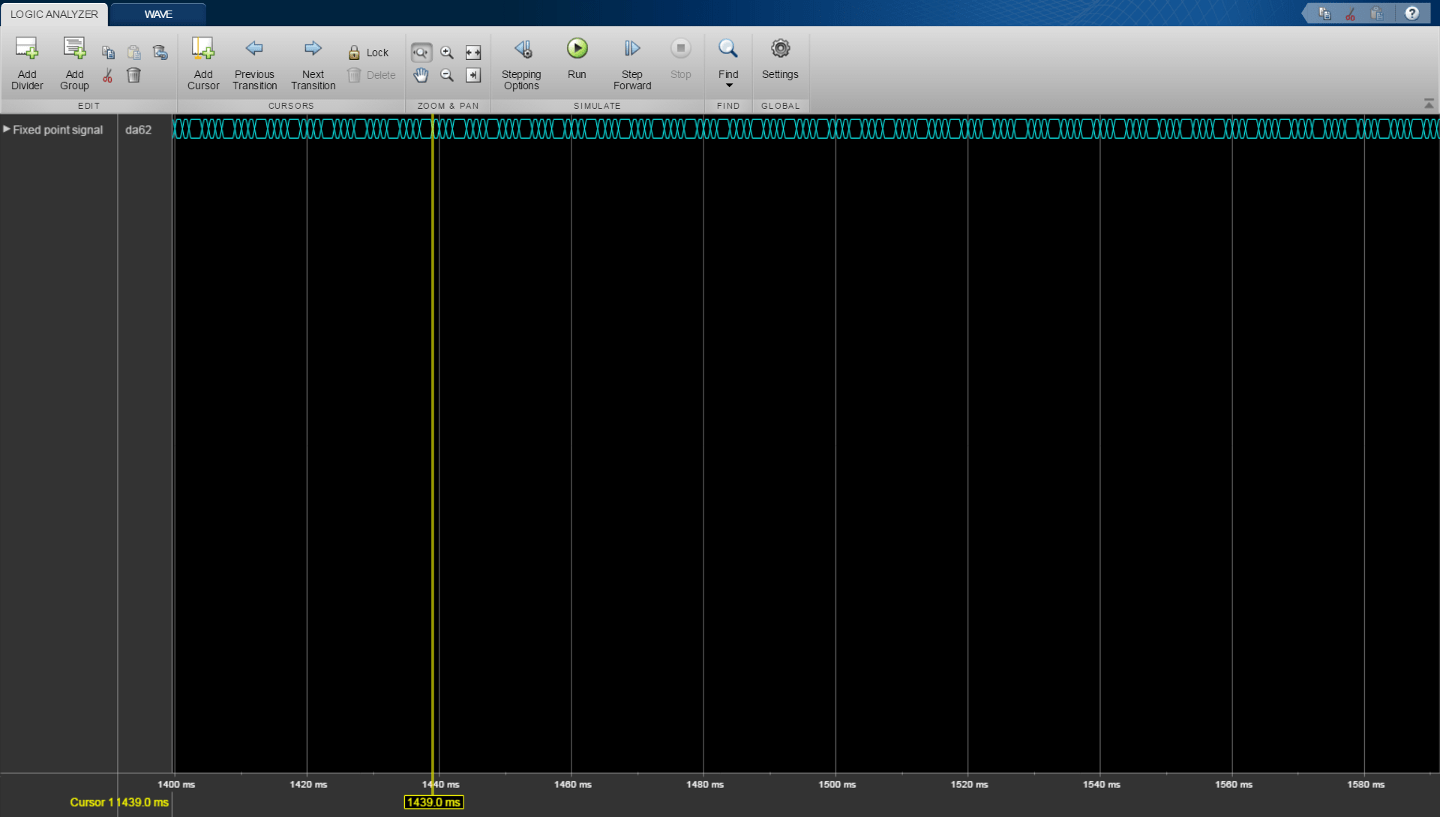

Graphical Settings

While the simulation is running, you cannot zoom, pan, or modify the trigger.

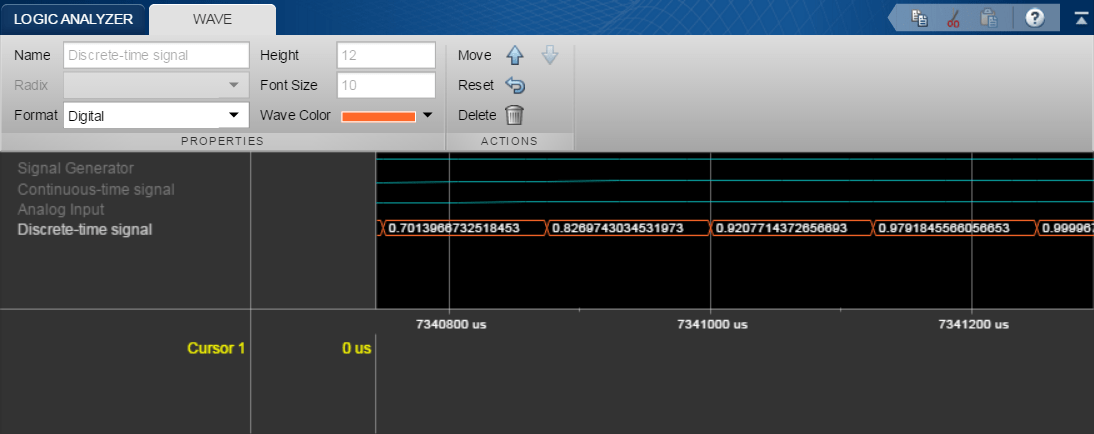

To visualize constant signals, in the settings, you must set the Format to

Digital. Constants marked for logging are visualized as a continuous transition.

| Mode | Supported | Notes and Limitations |

|---|---|---|

Normal | Yes | |

Accelerator | Yes | You cannot use the Logic Analyzer to visualize

signals in Model (Simulink) blocks

with Simulation mode set to

|

Rapid Accelerator | Yes | Data is not available in the Logic Analyzer during simulation. If you simulate a model with the simulation mode set to rapid accelerator, after simulation the following signals cannot be visualized in the Logic Analyzer:

|

Processor-in-the-loop (PIL) | No | |

Software-in-the-loop (SIL) | No | |

External | No |

For more information about these modes, see How Acceleration Modes Work (Simulink).

Version History

Introduced in R2016b