# Unleashing the Power of FPGAs through Model-Based Design

Nabeel Shirazi Senior Director System Level Design Tools

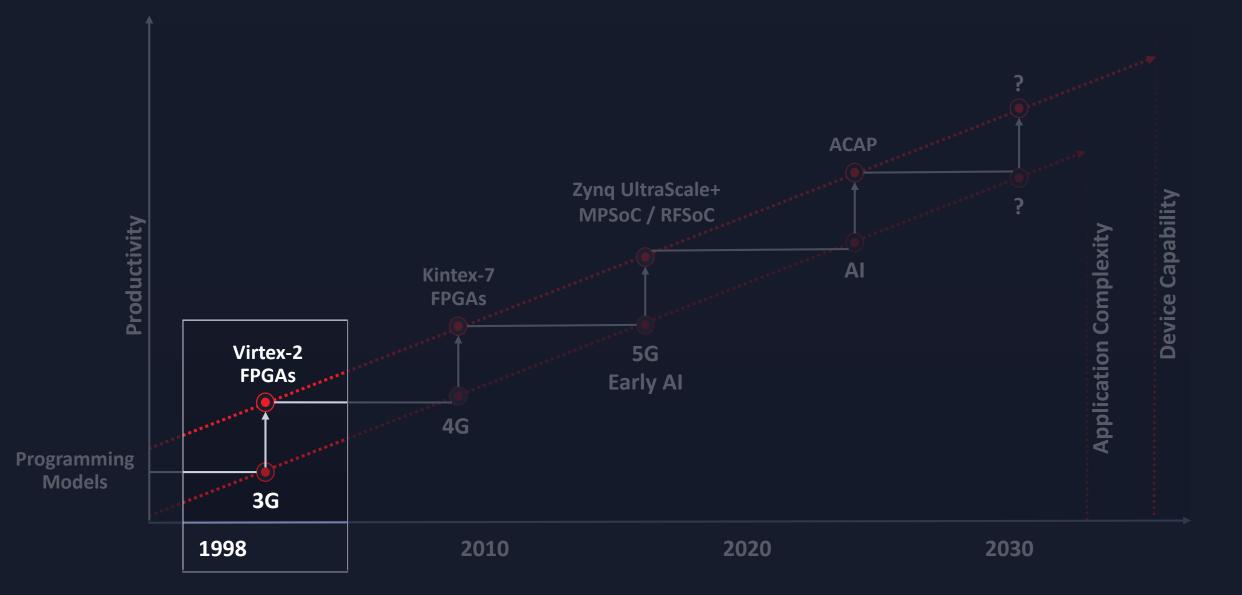

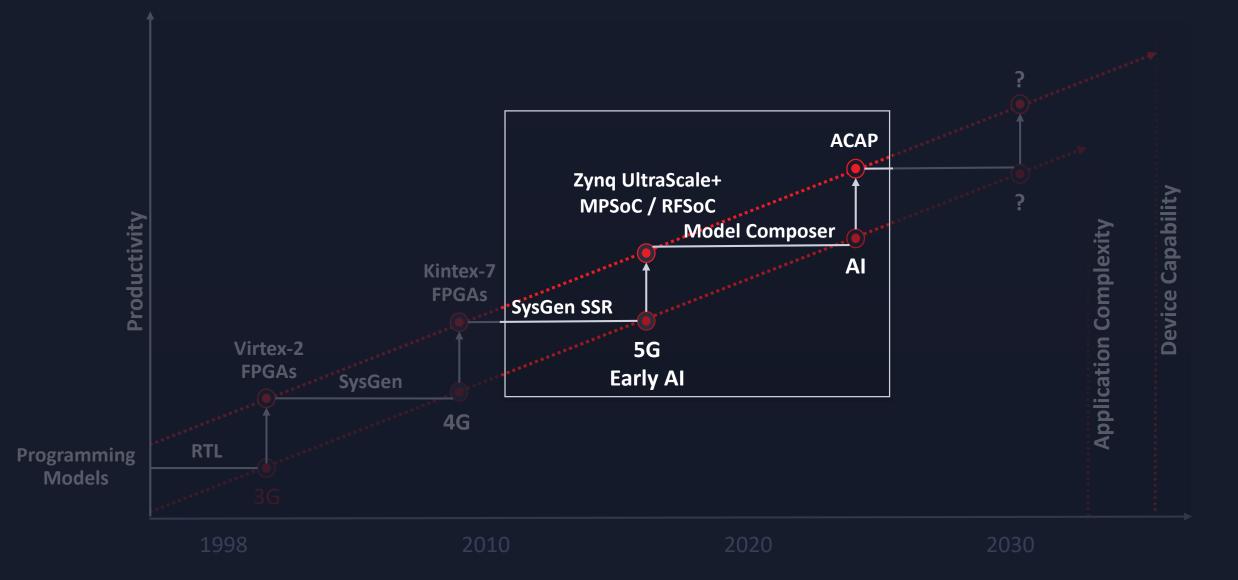

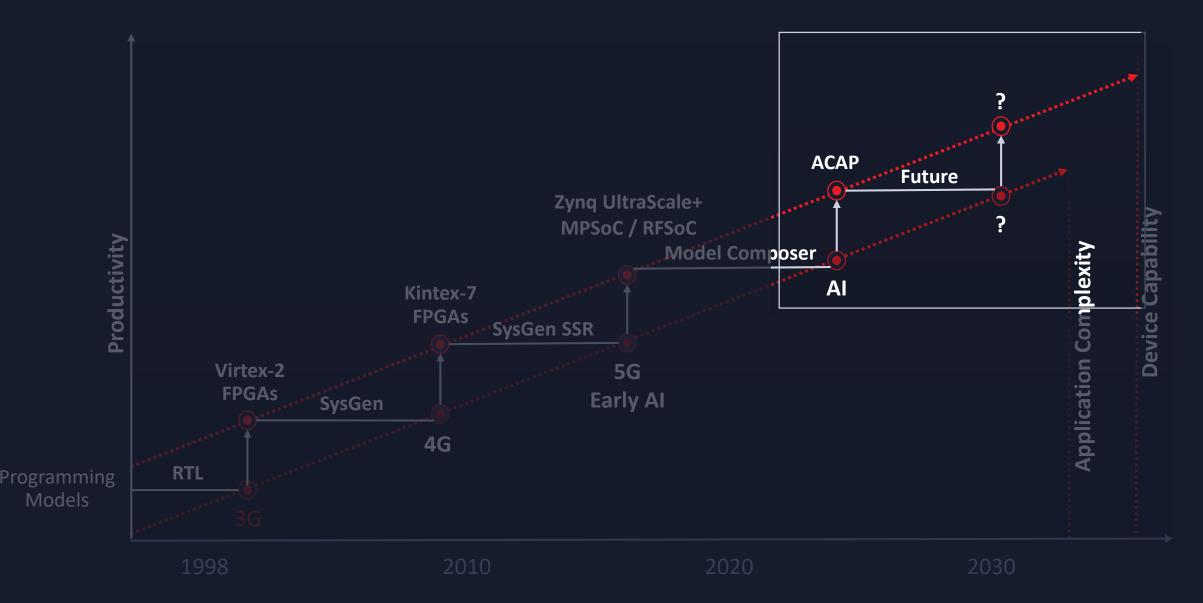

### Intersection of Applications, Devices, and Tools

# In the Beginning: FPGAs for 3G Wireless Radios

- Key application: Digital Baseband Pre-Distortion

- Enables use of cost effective non-linear power amplifiers

- Lowers spectral noise floor

- Why FPGAs:

- Custom memory hierarchy and parallel processing

- Enabled 3X cost reduction vs. analog implementations

- Programming Model:

- Simulink for algorithm development

- Traditional FPGA tools for implementation

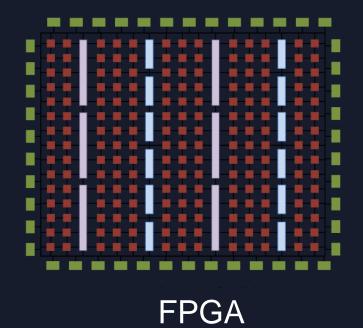

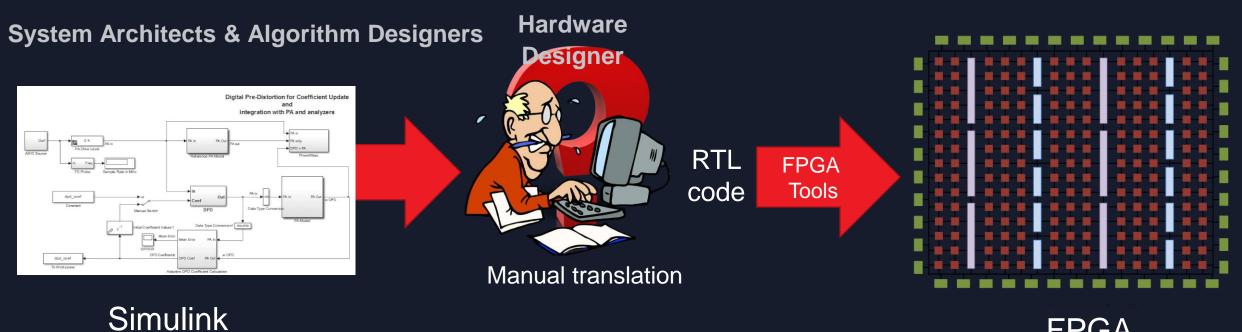

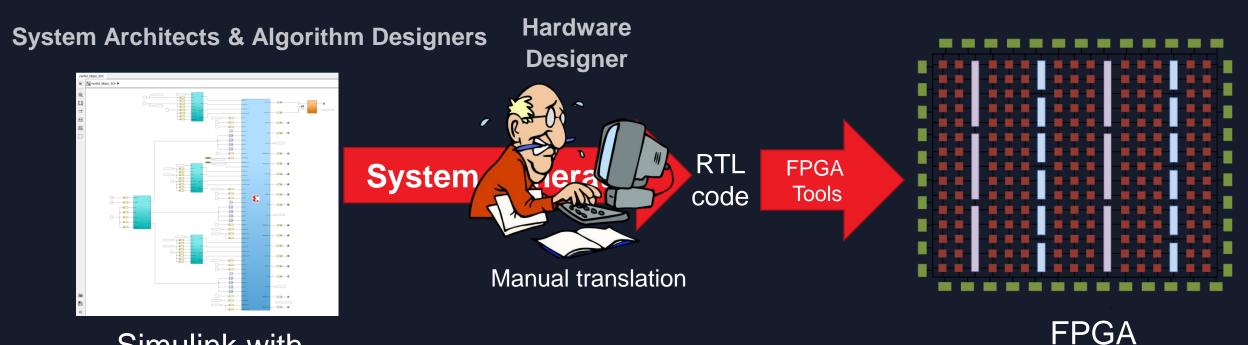

# Gap between Simulink and FPGAs

**FPGA**

# Bridging the Gap between Simulink and FPGAs

Simulink with Xilinx System Generator Blockset

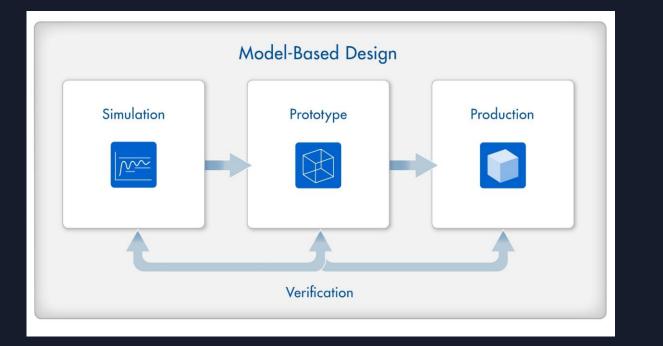

# > Why Model-Based Design

- Natural way to express parallelism

- Debug and test at the model level

- Reduce number hardware iterations

- Share models across different disciplines FPGA, RF, Communications

BAE Systems Achieves 80% Reduction in SW-defined Radio Development Time

645 hrs:

VHDL Expert using traditional design flow

VS.

46 hrs: Engineer with Simulink + System Generator flow

# Meeting Today's Challenges

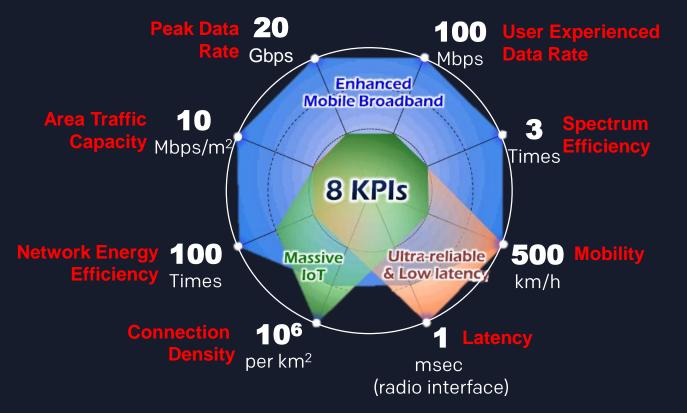

### 5G Wireless Radio Challenges

#### **5G Complexity is 100X 4G**

Still Evolving Standard

#### ETRI RWS-150029, 5G Vision and Enabling Technologies: ETRI Perspective 3GPP RAN Workshop Phoenix, Dec. 2015 http://www.3gpp.org/ftp/tsg\_ran/TSG\_RAN/TSGR\_70/Docs

New Technologies in 5G

- > Multi-user Massive MIMO

- > New beamforming technology

- > Millimeter wave transmission

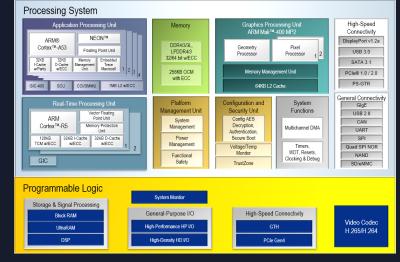

# Zynq RFSoC Devices for 5G Applications

**RFSoC Remote Radio Head** Wireless Backhaul Enabling Throughput for & Fixed Wireless Access Heterogeneous Multi-processing mmWave Transmission **Enabling Massive-MIMO** 2D Antenna Arrays **Processing System** DisplayPort Consumer USB 3.0 Endpoints Quad-Core Memorv SATA ARM® Sub-System Functions Cortex<sup>™</sup>-A53 PCIe® Gen2 GigE **5G** CAN Dual-Core Platform Config ARM® Management SPI Cortex<sup>™</sup>-R5 SD/eMMC NAND **Baseband Programmable Logic** Maximizing Throughput in Baseband Pools 33G 100G Cores PCIe® Gen4 UltraRAM Transceivers **RF-DAC RF-ADC SD-FEC** Analog-to-Digital Soft Decision **Digital-to-Analog** Converters Forward Converters Up to 4 GSPS Up to 6.4 GSPS Error Correction 0 e 8 = = =/••<del>8</del>==**0** 8--8 \*\*8=-

# > 5G Design in MATLAB & Simulink

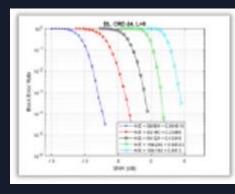

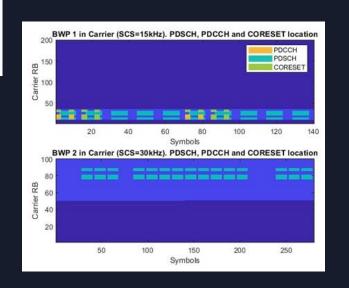

### 5G Toolbox

- End-to-End Link-Level Simulation

- Waveform Generation and Analysis

- Golden Reference Design Verification

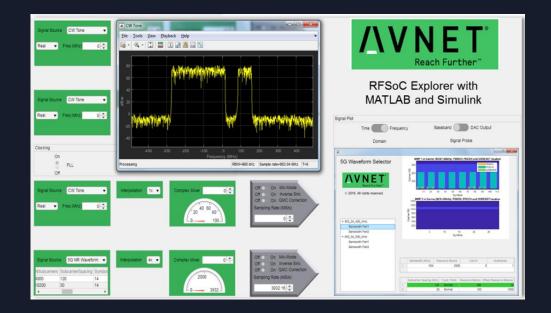

### Avnet RFSoC Explorer

- Generate stimuli

- Setup of device

- Analyze signals from H/W

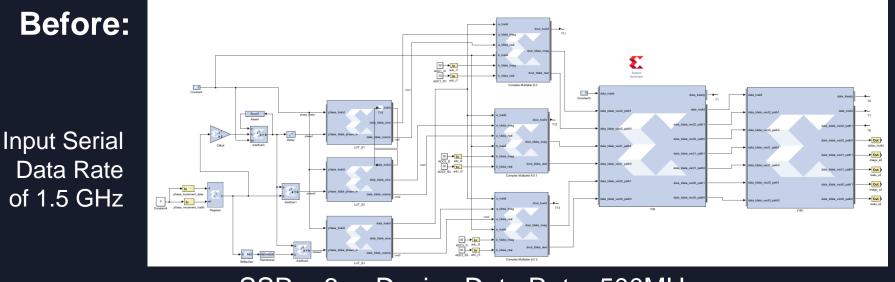

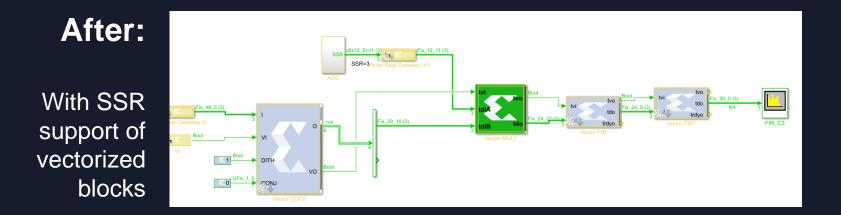

## Super Sample Rate Processing in SysGen

SSR = 3 Device Data Rate: 500MHz

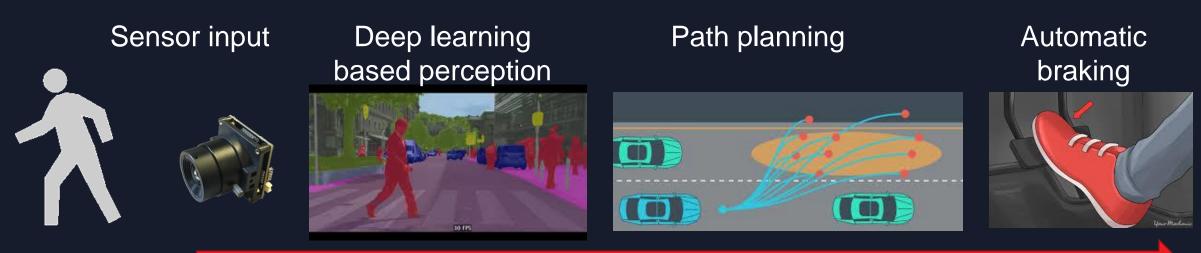

# Zynq MPSoC for Embedded Vision

Power budget: 5W

Cost budget: \$10-\$40

#### Zynq MPSoC

Driver Assistance Example:

Latency < 30 ms

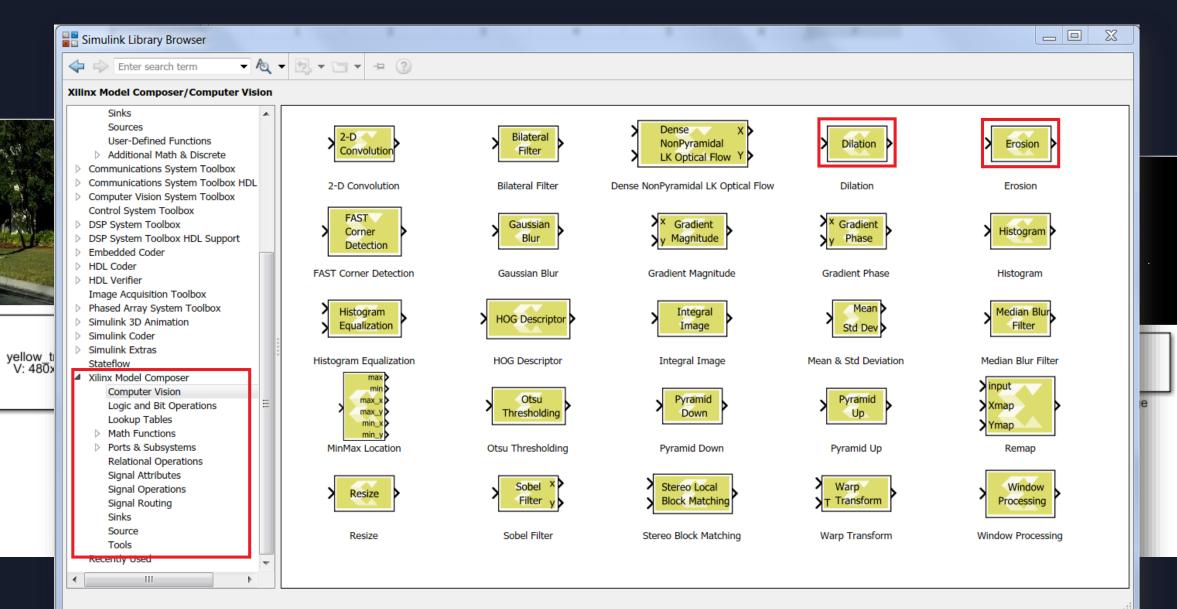

### Moving Up in Abstraction: Model Composer Blockset with OpenCV

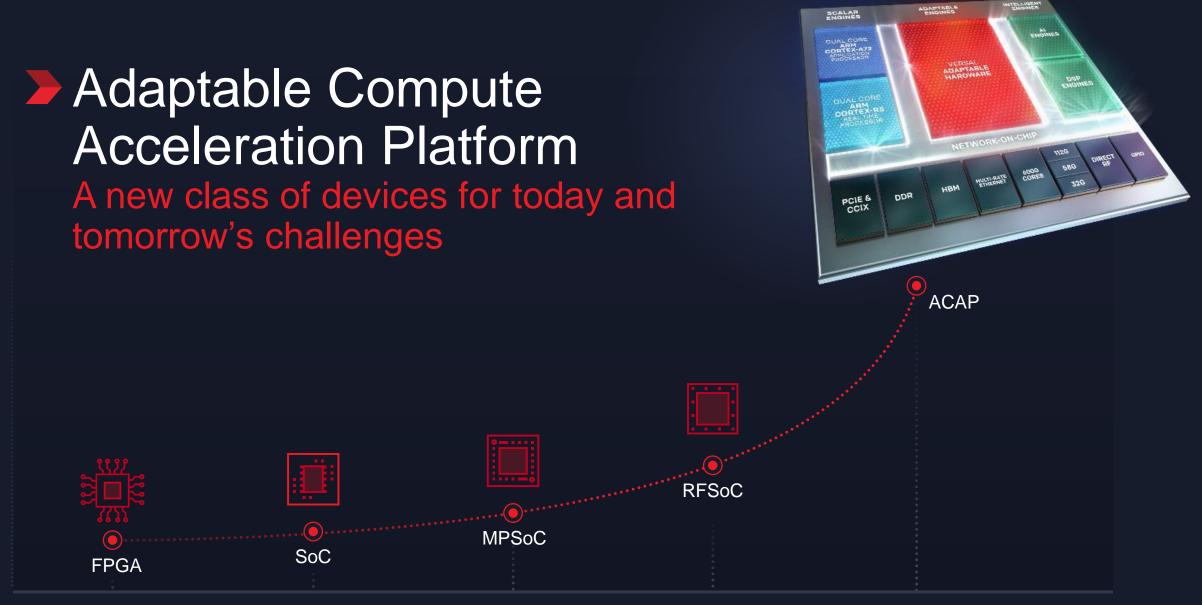

# The Road Ahead

### > AI, AI, and More AI

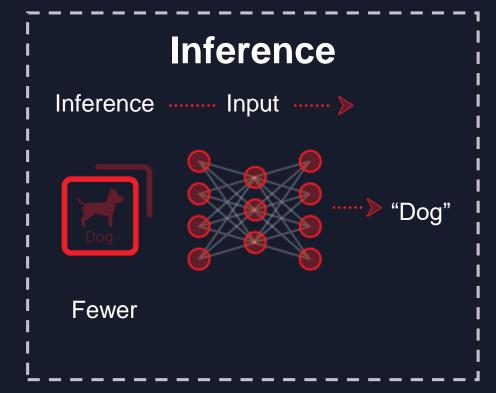

## AI/Machine Learning: Training vs. Inference

# Machine Learning Inference Challenges

### The rate of AI innovation

Performance at low latency

Low power consumption

Whole app acceleration

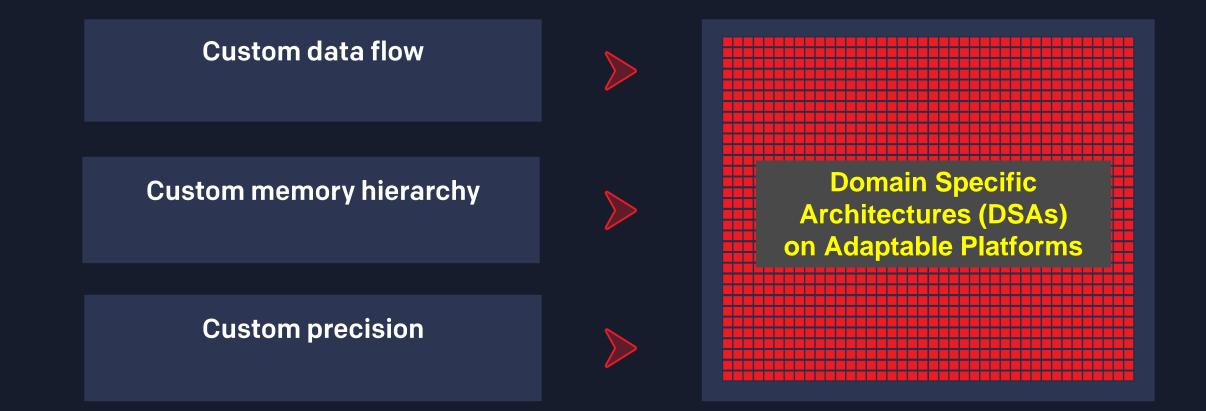

# Only Adaptable Hardware Addresses Inference Challenges

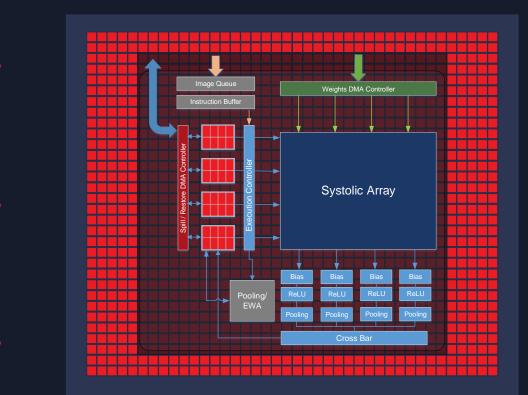

### Example Domain Specific Architecture: xDNN

Custom data flow Optimized for latest CNN

Custom memory hierarchy Optimized on-chip memory

> Custom precision Int8

Device Category

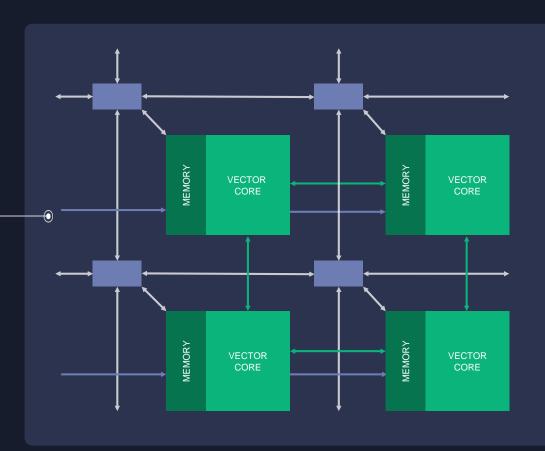

# > AI Engines

Optimized for AI Inference and Advanced Signal Processing Workloads

#### >1GHz VLIW/SIMD vector processor cores

- Massive array of interconnected cores with local memory

- Coupled to adaptable hardware enabling custom memory hierarchy

- Programmable with MATLAB/Simulink via Model Composer

### Low-Latency CNN Inference Performance

Sources: Alveo - Published (INT8); Versal - Projected (INT8), 65% PL reserved for whole application; GPU 1 - P4 Published (INT8); GPU 2 - V100 Published (FP16/FP32); GPU 3 - T4 Projected

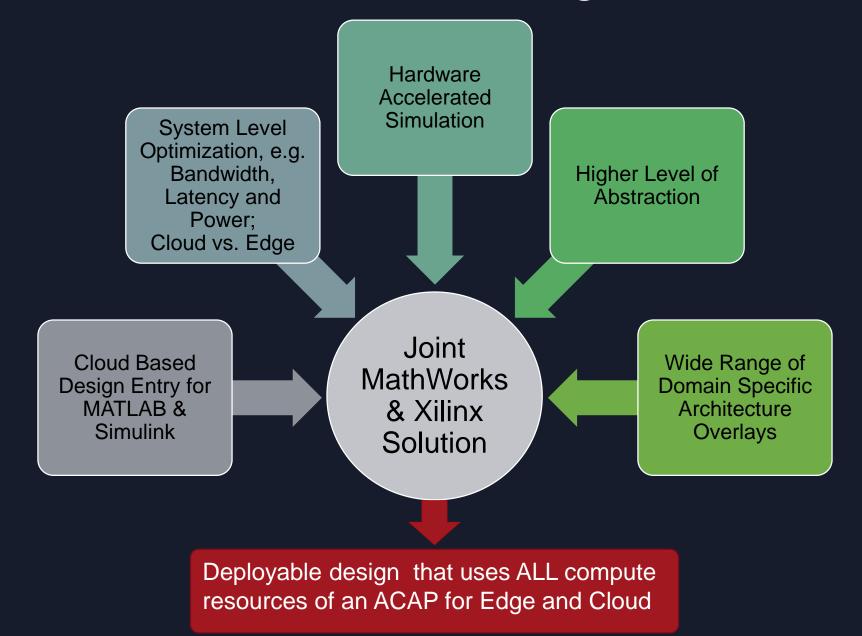

### Future of Model-Based Design for ACAPs

### Summary

Xilinx will continue to invest in Model-Based Design as a natural, productive on-ramp to our devices

Adaptable devices have a clear advantage in ML, ADAS and 5G to meet performance, latency and power requirements

The intersection of tools, silicon and platforms provides an inflection point for AI adoption